Förstå kraften i S-R-spärren: En port till modern elektronik

Spärrar är enkla digitala enheter som lagrar en bit information och håller det värdet tills det får nya insignaler.De används i digitala system för att tillfälligt hålla binära data.Spärrar kan göras med olika typer av grundläggande logiska grindar som och, eller inte, NAND och eller Gates.Den här artikeln undersöker design, funktion, variationer och användningar av S-R-spärren, och betonar dess bästa roll i modern elektronik och dess användning i praktiska kretsar och digitala logiksimuleringar.

Katalog

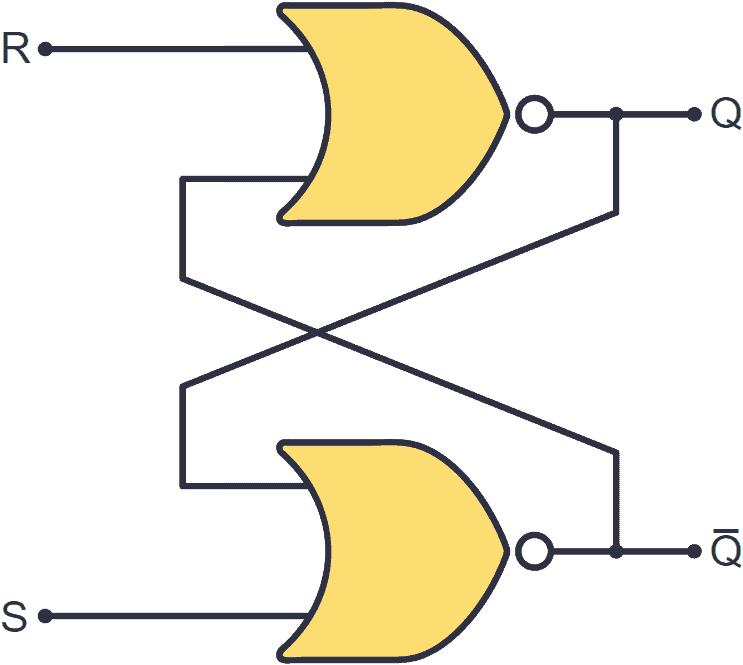

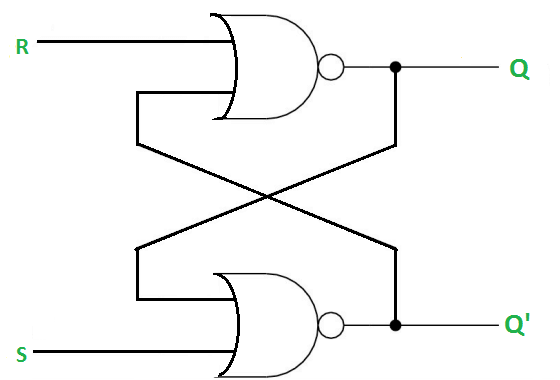

Bild 1: S-R spärrkretsdiagram

S-R-spärr

S-R (Set-Reset) spärren, en hörnsten i digital elektronik, är en bistable multivibrator.Den kan upprätthålla ett av två distinkta, stabila tillstånd på obestämd tid utan extern inmatning.Denna funktionalitet gör SR -spärren en huvudkomponent i minneslagrings- och växlingsoperationer över olika elektroniska enheter.

Strukturellt sett består SR -spärren av två sammankopplade eller grindar arrangerade i en återkopplingsslingdesign.Detta specifika arrangemang är viktigt eftersom den erbjuder förutsättningarna för bistabilitet.Varje NOR -portens utgång är direkt ansluten till ingången till den andra, vilket skapar en kontinuerlig slinga av feedback som ligger till grund för spärrets operation.

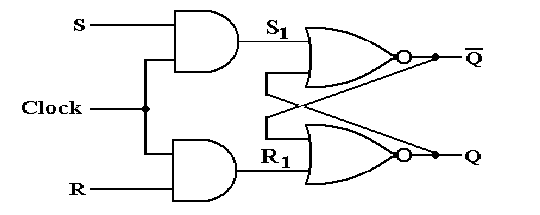

Bild 2: S-R-spärr och klocksignalen (CLK)

Utökning av den grundläggande designen introducerar den gated SR -spärren en extra ingång: klocksignalen (CLK).Denna förbättring innehåller en klockingång som ger lager av kontroll och integrerar spärroperationerna i system som kräver synkronisering.Denna synkronisering är skyldig när den bestämmer de exakta stunderna när spärren kan ändra tillstånd, lämpligt beskrivet av termen "gated".Införandet av klocksignalen säkerställer att förändringar i spärrets utgångstillstånd endast inträffar under den aktiva klockfasen, vanligtvis vid den stigande eller fallande kanten av CLK -signalen.

Införandet av CLK -ingången bevarar inte bara egenskaperna för den grundläggande SR -spärren utan anpassar också sin drift med den temporära dynamiken i större digitala system.Denna anpassning önskan om att upprätthålla dataintegritet och säkerställa att tillståndsövergångarna inträffar utan fel eller oavsiktliga förändringar, särskilt i komplexa kretskonfigurationer där flera spärrar kan interagera.Genom att kontrollera när spärren svarar på uppsättnings- och återställningskommandona kan systemet undvika problem som rasförhållanden och andra tidsrelaterade fel som annars kan störa systemstabilitet och prestanda.

Operativa tillstånd i S-R-spärren

Driften beror på ingångarna till två styrsignaler: SET (S) och RESET (R).Här förklarar vi hur dessa ingångar påverkar utgångarna och tillståndet för SR -spärren.

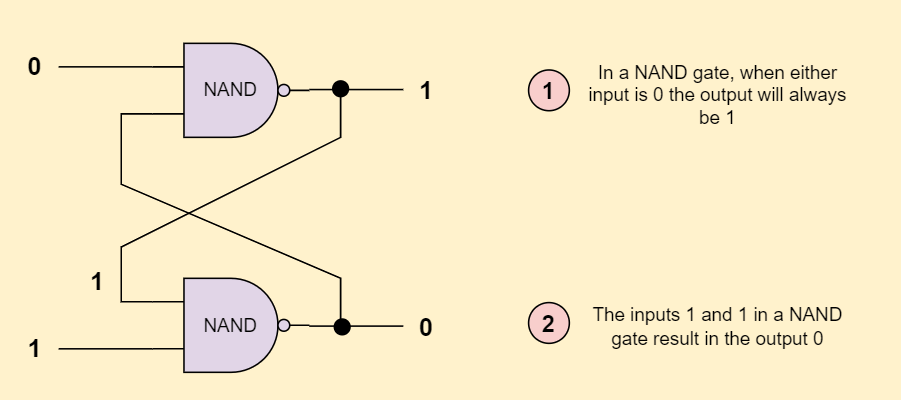

Fall 1: Ställ in villkor

När uppsättningen (erna) ingången är hög (1) och återställning (R) ingången är låg (0), kommer spärren in i det inställda tillståndet.I detta tillstånd kommer NAND-grinden ansluten till R-ingången att mata ut en låg signal på grund av den höga ingången från S. Denna låga signal orsakar den andra NAND-grinden att mata ut en hög signal, vilket ställer in Q till hög (1) och Q-bartill låg (0).Detta tillstånd är stabilt och kommer att hålla Q hög tills ingångarna ändras, vilket visar spärrens förmåga att lagra ett högt tillstånd.

Bild 3: Det inställda tillståndet

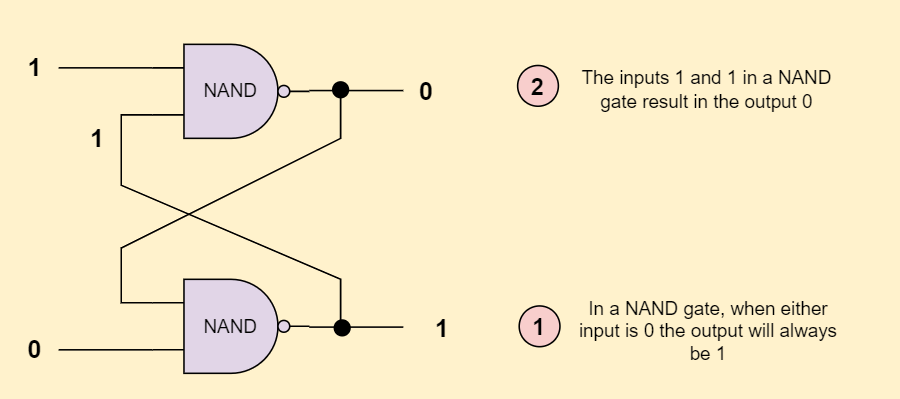

Fall 2: Återställ villkor

När S är låg (0) och R är hög (1) kommer spärren in i återställningstillståndet.Här gör den höga ingången på R och den låga ingången på S NAND -grinden ansluten till R -utgång till en låg signal.Denna låga signal sätter q till låga (0) och Q-bar till hög (1), vilket effektivt återställer spärren.Detta visar spärrens förmåga att återgå till ett stabilt lågt tillstånd i Q när de ges rätt ingångar.

Bild 4: Återställningstillståndet

Fall 3: Ogiltig tillstånd

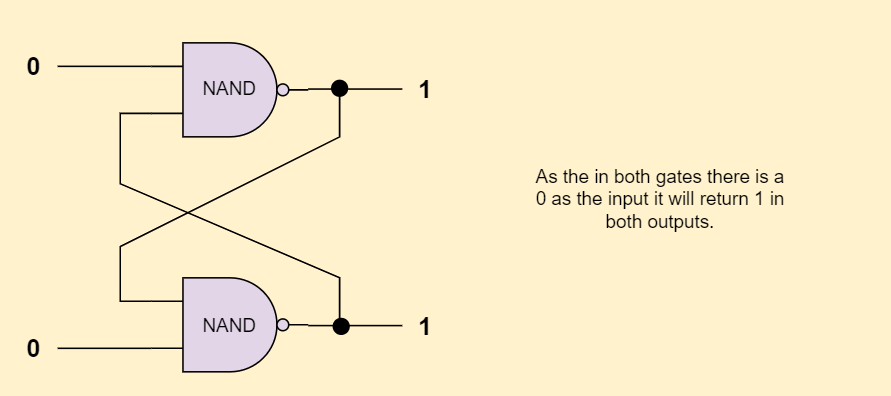

Om både S och R är låga (0) är båda ingångarna till NAND-portarna låga, vilket gör att båda utgångarna Q och Q-bar går högt.Detta tillstånd kallas ogiltigt eller förbjudet eftersom det bryter den grundläggande regeln att Q och Q-bar alltid ska vara motsatser.Detta scenario belyser SR -spärrets begränsning, och betonar vikten av att undvika sådana instabila tillstånd genom korrekt inputhantering.

Bild 5: Det ogiltiga tillståndet

Fall 4: Håll villkor

När båda ingångarna är höga (1) beror utgångarna på spärrets tidigare tillstånd snarare än de aktuella ingångarna.Detta är känt som hålltillståndet, där Q och Q-bar förblir oförändrade, och bevarar spärrets sista giltiga tillstånd.För vissa applikationer är det viktigt att kunna upprätthålla det spärrade tillståndet under långa perioder utan modifiering, såsom minneslagringsceller där dataintegritet är av stor betydelse.

Bild 6: Holdtillståndet

S-R spärr med en sanningstabell

Denna tabell är inte bara ett teoretiskt verktyg utan det är också praktiskt för både kretsdesigners och studenter.Det hjälper dem att se hur spärren uppträder under många förhållanden.Nedan presenterar vi den omfattande sanningstabellen för SR -spärren, följt av förklaringar och praktiska insikter för varje tillstånd.

|

S |

R |

Q |

Q-bar |

ANGE |

|

0 |

0 |

1 |

1 |

Ogiltig |

|

0 |

1 |

0 |

1 |

Återställa |

|

1 |

0 |

1 |

0 |

Uppsättning |

|

1 |

1 |

Q |

Q-bar |

Hålla |

Diagram 1: Sr

Spärre sanningstabell

Förklaring av varje rad

Ställ in tillstånd (s = 1, r = 0): Den här raden visar att när S är hög och r är låg, är Q inställd på hög (1) och Q-bar till låg (0).Detta speglar kretsens svar på ett inställt kommando och lagrar effektivt en '1'.

Återställningstillstånd (s = 0, r = 1): Här indikerar ingångarna en återställningsoperation.Följaktligen återställs Q till låg (0) och Q-bar är inställd på hög (1).Detta tillstånd visar spärrets förmåga att återgå till en '0'.

Ogiltigt tillstånd (S = 0, r = 0): Båda utgångarna blir höga i detta tillstånd, vilket i allmänhet undviks eftersom det resulterar i att båda utgångarna är identiska.Detta kan leda till instabilitet eller odefinierat beteende i spärren, eftersom det bryter mot regeln att Q och Q-bar alltid ska vara motsatser.

Håll tillstånd (s = 1, r = 1): I detta scenario upprätthåller spärren sitt tidigare tillstånd och visar sin förmåga att hålla det sista uppsättningen om inte uttryckligen beordras att förändras.

Praktiska insikter och tips

Förståelse av utgångar: Kom alltid ihåg att Q och Q-bar är idealiskt komplement.Varje avvikelse från denna regel (som ses i det ogiltiga tillståndet) indikerar ett problem eller felkonfiguration.

Undvik det ogiltiga tillståndet: Det är absolut nödvändigt att designers tar hand om att förhindra situationen där S och R är båda låga.Att implementera ytterligare logik eller låsningar kan hjälpa till att förhindra detta tillstånd.

Genom att använda hålltillståndet: Holdtillståndet kan vara särskilt bekvämt i applikationer som kräver datakonservering över tid.Att upprätthålla dataintegritet kan bero på att se till att spärren inte oavsiktligt går in i uppsättningen eller återställer tillståndet.

Tolkning av sanningstabellen: När du utformar eller felsöker kretsar, hänvisar till sanningstabellen för att förutsäga hur förändringar i ingången kommer att påverka utgången, särskilt i komplexa kretsar där flera spärrar används.

Funktionell dynamik i S-R-spärren

S-R (SET-RESET) spärren fungerar bra endast om dess ingångar hanteras korrekt.För att förstå hur det fungerar måste du veta hur olika ingångskombinationer påverkar utgångarna, Q och Q-bar (motsatsen till Q).

Bild 7: S-R-spärr

Om båda uppsättningarna (er) och återställningen (R) aktiveras samtidigt (S = 1 och R = 1), går spärren in i ett "förbjudet tillstånd", där båda utgångarna, Q och Q-bar, är 0.Detta är ett problem eftersom normalt sett bör Q och Q-bar vara motsatser.

Under normala förhållanden, för att ställa in spärren, aktiverar du S (inställda S till 1) och inaktivera R (inställt R till 0).Detta gör att Q går högt (1) och Q-baren går lågt (0), vilket visar att spärren kan lagra en 1. För att återställa spärren aktiverar du R (inställd R till 1) och inaktivera S (inställda S till 0).Detta gör att Q går lågt (0) och Q-bar går högt (1), vilket visar att spärren kan rensa sig själv och lagra en 0.

När båda ingångarna inaktiveras (s = 0 och r = 0), håller spärren sitt sista tillstånd, antingen inställd eller återställning.Detta är bra för att lagra data eller hålla ett tillstånd utan att behöva kontinuerlig input.

Rasförhållanden kan komplicera S-R-spärrens operation.Dessa fel inträffar när utgångarna förlitar sig starkt vid tidpunkten för ingångsändringar, vilket leder till oförutsägbara resultat om ingångarna ändras nästan samtidigt.För att förhindra detta och säkerställa att spärren fungerar pålitligt används ofta tidsfördröjningsmekanismer.Dessa förseningar ser till att en ingång aktiveras efter att den andra har haft tid att stabilisera.För att spärren ska användas i digitala kretsar där exakt tidpunkt krävs måste den fungera konsekvent och upprätthålla stabila utgångar.Detta möjliggörs av den kontrollerade tidpunkten.

Logikdiagram över S-R-spärr

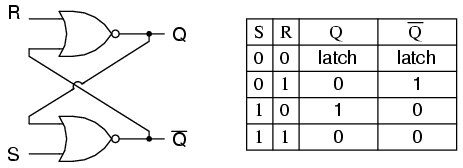

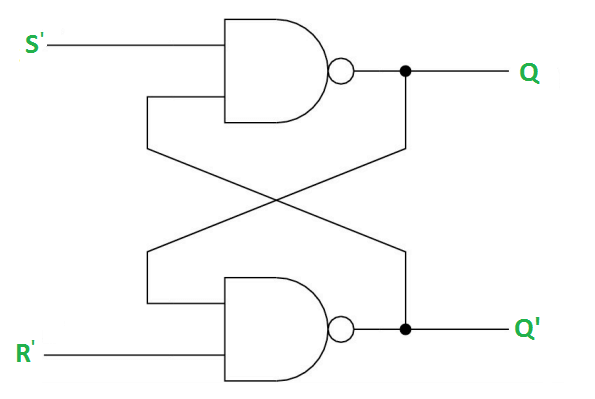

SR -spärren är en grundläggande sekventiell logikkrets med två huvudkonfigurationer: NOR eller NAND -grindar.Varje installation påverkar hur spärren fungerar och svarar på ingångar, vilket möjliggör anpassning för olika elektroniska applikationer.

Bild 8: Logikdiagram representerar S-R-spärren med NAND GATE

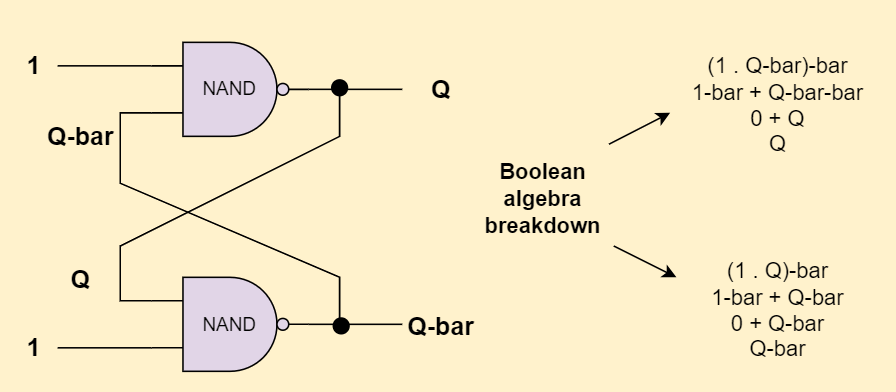

Implementering med NAND -grindar

När du bygger en SR -spärr med NAND -grindar används en återkopplingsslinga för att upprätthålla sitt tillstånd.Denna inställning gör det möjligt för spärren att hålla sitt tidigare tillstånd när både ingångar (S och R) är låga.NAND -grindar matar ut högt såvida inte båda ingångarna är höga.Spärrets tillstånd förändras när en ingång är hög och den andra är låg.Det är bäst att undvika att ställa in både S och R högt samtidigt eftersom detta tvingar båda utgångarna att gå lågt, vilket leder till ett odefinierat tillstånd där utgångarna inte längre är komplementära.Korrekt ingångshantering är ett måste för att förhindra instabilitet i NAND-baserade SR-spärrar.

Implementering med NOR -grindar

Att använda NOR -grindar för en SR -spärr ändrar de operativa förhållandena jämfört med NAND -grindarna.I denna konfiguration har spärren sitt tillstånd när båda ingångarna är höga.Spärren ändrar tillståndet när en ingång är låg och den andra är hög.Inte heller grindar utmatar endast om båda ingångarna är låga.Denna installation är användbar i kretsar där standardtillståndet är att ha båda utgångarna låga, vilket säkerställer förutsägbar utgång under höga ingångsförhållanden.Det är emellertid bäst att undvika att ställa in båda ingångarna låga samtidigt, eftersom detta orsakar motstridiga utgångar och minskar spärrens tillförlitlighet.

Bild 9: Logikdiagram representerar S-R-spärr med NOR-grind

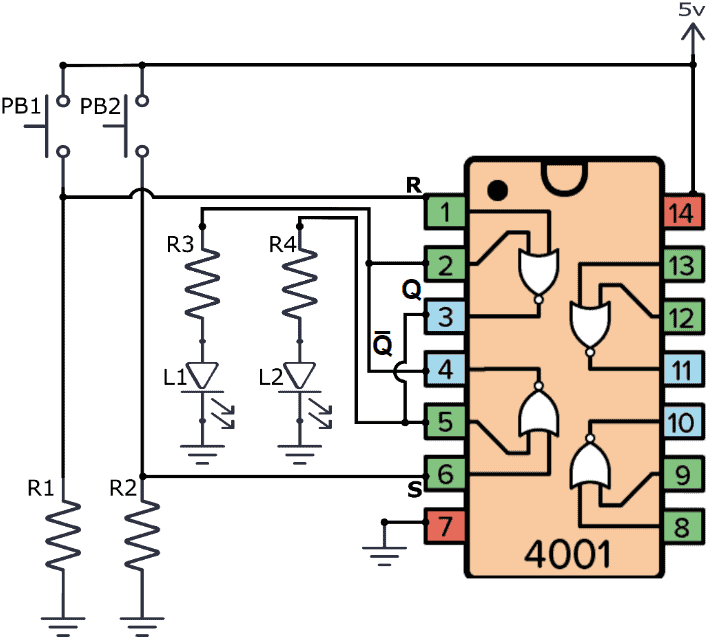

Exempelkrets

Att utforska hur SR -spärrar fungerar i verkliga livet visar deras användbarhet.Ett bra exempel är en krets som använder CD4001 -chipet, som har fyra eller grindar.Denna krets visar hur SR -spärrar kan styra enheter som lysdioder med enkla åtgärder som att trycka på knappar.

I det här exemplet är NOR -grindarna i CD4001 -chipet inställt för att göra en SR -spärr.Två grindar är anslutna i en återkopplingsslinga för att hålla spärrtillståndet.Tryckknappar läggs till i kretsen som ingångar för uppsättning och återställning.Om du trycker på en knapp ändrar ingångens tillstånd, vilket ändrar spärren och LED -tillståndet.Till exempel, att trycka på set -knappen tänds lysdioden, och den förblir tänd även efter att knappen har släppts, vilket visar hur spärren kan hålla ett tillstånd.

För att göra kretsen bättre kan fler lysdioder läggas till för att visa utgångstillståndet för både Q och Q-bar.Detta gör det lättare att se hur spärren fungerar, vilket är till stor hjälp i inlärningsmiljöer.

Bild 10: S-R-spärr med CD4001-chipet

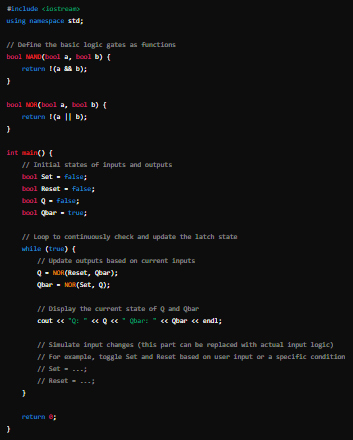

Kodimplementering

Att översätta den operativa logiken för en SR -spärr till programvara visar hur digital logikdesign kan fungera både i hårdvara och i virtuella simuleringar.Att använda ett programmeringsspråk som C ++ är effektivt eftersom det stöder den komplexa logik och kontroll som behövs för att imitera hårdvarubeteenden.

För att göra en SR -spärr i C ++ börjar du med att definiera de grundläggande logikgrindarna som funktioner som fungerar som deras hårdvaruversioner.Till exempel skulle en NAND -grindfunktion returnera motsatsen till och operationen på dess ingångar.På liknande sätt skulle en eller grindfunktion returnera motsatsen till OR -operationen.Med dessa grundläggande funktioner kan du modellera SR -spärrens beteende genom att skapa en återkopplingsslinga mellan dessa grindfunktioner, baserat på spärrens kretsschema.

Koden skulle vanligtvis ha en slinga som kontinuerligt kontrollerar tillstånden för ingångarna (inställda och återställningar) och uppdaterar utgångarna (Q och Q-bar) i enlighet därmed.Villkorliga uttalanden i denna slinga avgör hur förändringar i ingången påverkar utgångarna, och imiterar SR -spärrens fysiska beteende nära.Till exempel, om både inställda och återställer ingångar är låga, förblir utgångarna desamma.Om inställningen är hög och återställningen är låg blir utgången Q hög och Q-bar blir låg, vilket replikerar spärrens inställda tillstånd.

Här är ett enkelt exempel på hur detta kan se ut i kod:

Bild 11: SR -spärr i C ++

Den här koden sätter upp en enkel SR -spärr med NOR -grindar och kontrollerar och uppdaterar kontinuerligt spärrtillståndet baserat på ingångarna.

SR -spärr

Kontrollsystem i motoroperationer: SR -spärren som krävs av system för motorstyrning.Med hjälp av start (er) och stopp (R) tryckknappsbrytare håller SR -spärren en motor igång även efter att startknappen har släppts.Denna installation säkerställer att motorn går kontinuerligt tills den stoppas, vilket förbättrar säkerheten och bekvämligheten.

Minnes- och datalagring: När du skapar större minneskretsar spelar SR -spärren en roll eftersom den kan lagra en enda bit data.Den upprätthåller data i ett stabilt tillstånd tills det uppdateras, vilket utgör grunden för minnesceller i digital datoranvändning.

Signalkontroll och hantering: I kontrollsignalapplikationer har SR -spärrar specifika bitar tills vissa villkor är uppfyllda, vilket säkerställer korrekt sekvens och tidpunkt i operationer.Precision vid signalbehandling och dataflöde beror på detta.

Debouncing -kretsar: SR -spärrar stabiliserar signaler från mekaniska omkopplare och knappar, vilket förhindrar falsk utlösning och fel orsakade av "studs" när omkopplare trycks in.Detta passar särskilt i digitala gränssnitt som tangentbord.

Grundläggande element i digitala system: Utformningen av flip-flops och räknare, som är lämpliga för timing och sekvensering i elektronik, förlitar sig starkt på SR-spärrar.De används också som pulsspärr för snabba tillstånd.

Specialiserade applikationer: I asynkrona system används variationer som D -spärren för säker och pålitlig dataöverföring.I synkrona tvåfas-system minskar datavalet transitantalet, förbättrar effektiviteten och minskar förseningen.

Bredare implikationer i elektronik: SR -spärrar används allmänt i kraftgrindningskretsar och spelar en roll i energibesparing inom elektroniska apparater.De hanterar krafttillstånd på en detaljerad nivå och bidrar till den totala energieffektiviteten för digitala system.

Slutsats

S-R-spärren visar vikten av enkla logikstrukturer i komplexa digitala system.Genom att titta på dess olika inställningar och hur det fungerar ser vi att S-R-spärren håller data stabila och gör systemen effektiva och pålitliga.Det kan fungera under olika förhållanden, som visas med sanningstabeller och logiska diagram, vilket gör det anpassningsbart för flera användningsområden, från motorisk kontroll till grundläggande digitala kretsar som flip-flops och räknare.S-R-spärren är lämplig i många praktiska tillämpningar, såsom minnesceller i datorer och avlägsnar kretsar i digitala gränssnitt, förbättrar effektiviteten och minskar fel i elektroniska enheter.Med återkopplingsmekanismer och noggrann inmatningssignalhantering är S-R-spärren bra för att utforma mer pålitliga och effektiva digitala system.Att studera sin funktion genom programvarusimuleringar hjälper till att ansluta teoretisk elektronik med verkliga applikationer, vilket gör S-R-spärren till ett viktigt ämne för både nya och erfarna elektroniska ingenjörer.

Vanliga frågor [FAQ]

1. Vad är syftet med SR -spärren?

SR -spärren används för att lagra en enda bit data;Det är en grundläggande form av minne i digitala kretsar.Dess huvudfunktion är att behålla tillståndet för lite tills det ändras med insignaler.

2. Är SR -spärren aktiv hög eller låg?

SR -spärren är vanligtvis aktiv hög, vilket innebär att den svarar på höga ingångar (logiknivå 1).När ingångarna S (set) och R (återställning) är höga, utlöser de förändringar i utgången.

3. Vad är nackdelen med en SR -spärr?

En stor nackdel med SR -spärren är dess mottaglighet för ett ogiltigt tillstånd där både uppsättnings- och återställningsingångarna är höga samtidigt.Denna situation leder till en odefinierad produktion, vilket kan resultera i opålitligt eller oförutsägbart beteende.

4. Vilka är reglerna för SR -spärren?

Om S (set) är hög och R (återställning) är låg, är utgången Q inställd på hög.

Om R är hög och S är låg återställs utgången Q till låg.

Om både S och R är låga behåller utgången sitt tidigare tillstånd.

Om både S och R är höga är utgången odefinierad eller ogiltig.

5. Vad är minne i SR -spärren?

Minnet i en SR -spärr hänvisar till dess förmåga att upprätthålla utgångstillståndet (högt eller lågt) på obestämd tid tills det får input för att ändra tillståndet.Detta gör det till en bistabil enhet, perfekt för enkel minneslagring.

6. Vilka är utgångarna från SR -spärren?

SR-spärren har två utgångar, q och q '(Q-bar).Q representerar det nuvarande tillståndet, medan Q 'är det omvända av Q. När Q är hög är Q' låg och vice versa.

7. Var använder vi spärr?

När kortvarig datalagring eller tillståndsbehållning krävs används spärrar i olika typer av applikationer.Detta inkluderar datalagring i flip-flops, register och minnesenheter samt i system som kräver datasynkronisering och kretshållfunktioner.