HembloggSR Flip-Flop Knowledge Guide-Arbetsprincip, fördelar, nackdelar, sanningstabell och skillnader från RS-flip-flop

SR Flip-Flop Knowledge Guide-Arbetsprincip, fördelar, nackdelar, sanningstabell och skillnader från RS-flip-flop

En flip-flop är helt enkelt en term som hänvisar till en digital elektronisk enhet, som är en elektronisk komponent som används för att lagra en enda information.

SR-flip-flop (inställning av flip-flop) är en grundläggande komponent i digitala elektroniska kretsar som används för att lagra och manipulera data.Det fungerar på ett sekventiellt sätt.SR-flip-flops kan konstrueras med SR-spärrar.En spärr är en digital elektronisk krets som tar den enkla formen av ett lagringselement, som kan lagra en bit binär information (0 eller 1).I den här artikeln kommer vi att diskutera SR-flip-flop, inklusive dess arbetsprincip, sanningstabell, fördelar, nackdelar och skillnader från RS-flip-flop.

Katalog

1. SR-flip-flop arbetsprincip

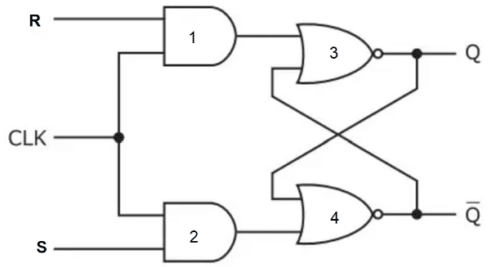

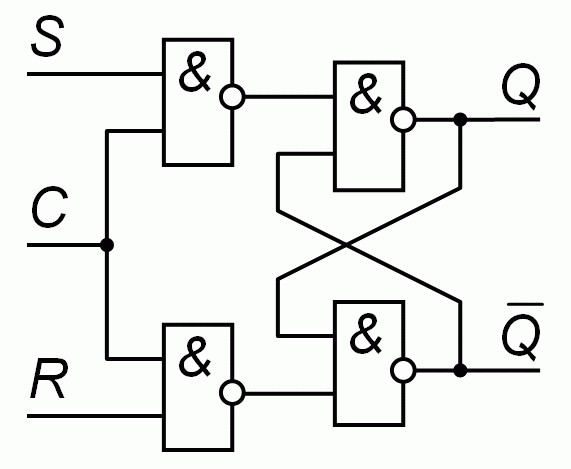

Den enklaste RS-flip-flopen kan byggas med två 2-ingångar eller grindar, som visas i diagrammet:

Observera att hur elementen är anslutna säkerställer att de alltid är i motsatta stater.Om utgången från det första elementet är 1 kommer utgången från det andra elementet att vara 0 och vice versa.

För att underlätta förståelse är här de fyra scenarierna som kan uppstå med en SR-flip-flop:

Scenario 1: S = 0, r = 0

GATE -utgång: Både GATE1 och GATE2 -utgång 0. Tillståndsunderhåll: Eftersom grindarna 3 och 4 är eller grindar, med en ingång vid 0 beror deras utgångar på den andra ingången.Således behåller Gate3/Q (n+1) det tidigare tillståndet Q, och GATE4/Q (n+1) 'behåller det komplementära tillståndet q'.

Scenario 2: S = 0, r = 1

GATE Output: GATE1 Utgångar 1 (Eftersom R är hög) utgångar GAT2 0. Återställ drift: För GATE3 är en ingång hög (från GATE1), vilket leder till en utgång på 0 via NOR -operationen och återställer således tillståndet.En ingång till Gate4 förblir emellertid låg, utgång 1, vilket indikerar det komplementära tillståndet.

Scenario 3: S = 1, r = 0

Gate Output: GATE1 Utgångar 0, GATE2 Utgångar 1 (eftersom S är hög).Ställ in drift: För närvarande matar ut GATE3 1 (den andra ingången från GATE1 är låg), vilket ställer in flip-flop.Omvänt, på grund av den höga ingången från GATE2, utgångar GAT4 0, vilket bekräftar det komplementära tillståndet.

Scenario 4: S = 1, r = 1

GATE Output: Med båda ingångarna höga, båda grindarna utmatning 1. Ogiltigt tillstånd: När båda ingångarna är höga bör grindarna 3 och 4 båda utgången 0, vilket resulterar i en konflikt eftersom Q (n+1) och Q (n+1) 'Var komplementära utgångar, men detta är inte fallet, vilket leder till att detta tillstånd är ogiltigt.

2. SR flip-flop sanningstabell

|

S |

R |

Q (n+1) |

Ange |

|

0 |

0 |

Qn |

Ingen förändring |

|

0 |

1 |

0 |

ÅTERSTÄLLA |

|

1 |

0 |

1 |

UPPSÄTTNING |

|

1 |

1 |

X |

OGILTIG |

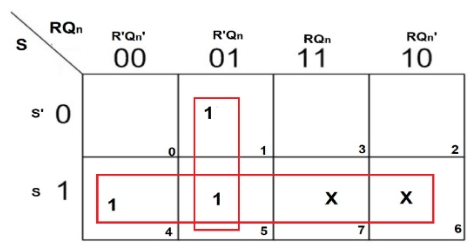

Vi kommer att använda denna sanningstabell för att skriva den karakteristiska tabellen för SR-flip-flop.I sanningstabellen kan du se två ingångar, s och r och en utgång, q (n+1).Men i den karakteristiska tabellen kommer du att se tre ingångar, S, R och QN och en utgång, Q (n+1).

Från logikdiagrammet är det uppenbart att Qn och Qn 'är två komplementära utgångar, som också fungerar som ingångar till grindarna 3 och 4, så vi betraktar QN, det aktuella tillståndet för flip-flop, som en ingång och Q (N+1), nästa tillstånd, som en utgång.

Efter att ha skrivit den karakteristiska tabellen kommer vi att rita en 3-variabel K-map för att härleda den karakteristiska ekvationen.

3. Karakteristisk tabell

|

S |

R |

Qn |

Q (n+1) |

|

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

X |

|

1 |

1 |

1 |

X |

Från K-kartan får du två par.Efter att ha löst båda får vi följande karakteristiska ekvation:

Q (n + 1) = s + r'qn

4. Fördelar med SR-flip-flop

Att använda SR-flip-flops har flera fördelar.Nedan följer några av dem:

- Enkelhet: Utformningen av SR-flip-flops är relativt enkel och består endast av några få grindar.De kan enkelt integreras i större kretsar utan att komplicera den övergripande designen.

- Hastighet: SR-flip-flops fungerar med hög hastighet.De kan snabbt växla mellan set- och återställningsstillstånd utan fördröjning, vilket säkerställer att digitala system kan utföra uppgifter mer effektivt och därmed förbättra prestandan hos tekniker som förlitar sig på snabb databehandling.

- Låg effektförbrukning: SR-flip-flops konsumerar mycket liten kraft, vilket gör dem idealiska för användning i batteridrivna enheter, såsom mobiltelefoner och bärbara datoranordningar, samtidigt som de innebär lägre driftskostnader när det gäller energianvändning.

- Bistable Operation: SR Flip-flops kan på obestämd tid upprätthålla ett tillstånd (inställt eller återställning) tills en insignal uppmanar en förändring, och förmågan att upprätthålla ett stabilt tillstånd utan konstant inmatning gör SR-flip-flops användbara för olika applikationer.

5. Begränsningar av SR-flip-flops

Trots flera fördelar har SR-flip-flops också vissa begränsningar.Nedan följer några av dem:

- Rasförhållanden: SR-flip-flops är mottagliga för tävlingsförhållanden där utgångstillståndet kan förändras oförutsägbart på grund av förändringar i tidpunkten för insignaler, vilket potentiellt kan leda till fel eller oväntade resultat.

- Ogiltigt tillstånd: En inneboende begränsning av SR-flip-flops är deras beteende när både uppsättningen (erna) och återställning (R) är aktiva samtidigt.I detta fall kommer vipploppet in i ett ogiltigt tillstånd, vilket ofta resulterar i att båda utgångarna är höga eller låga, vilket bryter mot den grundläggande driftsprincipen för en bistable-enhet.Detta ogiltiga tillstånd kan störa den normala funktionen hos digitala kretsar, vilket leder till oförutsägbart systembeteende och potentiell dataförlust.

- Begränsad skalbarhet: SR-flip-flops kan vara svårt att skala till mer komplexa digitala system när systemets komplexitet ökar, sannolikheten för att införa fel på grund av den grundläggande karaktären hos SR-flip-flops ökar också.

6. Ansökningsområden

- Kontrollsystem: I kontrollsystem kan SR-flip-flops uppnå smidiga övergångar mellan signaler, vilket minimerar olycksriskerna och förbättrar trafikflödet.En vanlig applikation finns i trafikljuskontrollsystem, där SR-flip-flops hjälper till att hantera sekvensen för trafikljus, vilket säkerställer att signaler förändras på ett exakt och ordnat sätt, och därmed säkert och effektivt kontroll av trafikflödet.

- Minneslagring: SR-flip-flops är också grundläggande komponenter i minneslagringsenheter som register.De används för att tillfälligt lagra data i datoranordningar från mikroprocessorer till digitala signalprocessorer, vilket möjliggör snabb åtkomst och manipulation av data under bearbetningsuppgifter.

- Digitala räknare: SR-flip-flops används i digitala räknare för att räkna operationer, vilket möjliggör ökning eller minskning baserat på insignaler.

- Datasynkronisering: SR-flip-flops är avgörande för att synkronisera datasignaler mellan två digitala kretsar, vilket säkerställer att de fungerar samtidigt inom samma klockcykel, vilket är till stor hjälp för att upprätthålla tillförlitligheten i kommunikationsnätverk.

- Oscillatorer: När de kombineras med andra komponenter kan SR-flip-flops bilda enkla oscillatorer som producerar periodiska signaler.Detta är särskilt användbart i applikationer som klockkretsar och ljudsignalgeneratorer där konsekvent och stabil signalgenerering behövs.

7. Skillnader mellan SR och RS flip-flops

|

Särdrag |

SR-flip-flop |

RS flip-flop |

|

S = 0 , r = 0 |

Q State (ingen förändring) upprätthålls. |

Q State (ingen förändring) upprätthålls. |

|

S = 0 , r = 1 |

Återställning (q = 0) |

Återställning (q = 0) |

|

S = 1 , r = 0 |

Set (q = 1) |

Set (q = 1) |

|

S = 1 , r = 1 |

Set (dominerande) (q = 1) |

Återställ (dominerande) (Q = 0) |

|

Fördelar: |

När S och R är båda 1, är den inställda operationen

har företräde. |

När S och R är båda 1, återställs återställningsoperationen

har företräde. |