Behärskning av SR -spärrar: symboler, funktioner och praktiska applikationer

En SR -spärr är en asynkron krets som fungerar oberoende av klocksignaler, vilket gör det till ett mångsidigt verktyg i olika applikationer.Det upprätthåller ett binärt tillstånd - antingen högt (1) eller låg (0) - och kan lagra en enda bit information, som den har tills nya insignaler dikterar en förändring.Detta grundläggande binära lagringselement är konstruerat med två tvärkopplade logikgrindar, vanligtvis eller Nand-grindar.Uppsättningsingångarna aktiverar spärren och ställer in utgången (q) till hög, medan återställningsingången (R) ställer in utgången till låg.Men samtidiga höga signaler på båda ingångarna leder till ett odefinierat tillstånd, måste ett tillståndsdesigners undvika.SR -spärrar är inte bara teoretiska konstruktioner;De implementeras i praktiska system för att hålla tillfälliga data, stödja mellanliggande bearbetningsresultat och till och med hantera feldetektering i kritiska tillämpningar som flyg- och medicintekniska produkter, som visar deras oumbärbarhet i digital kretsdesign.Katalog

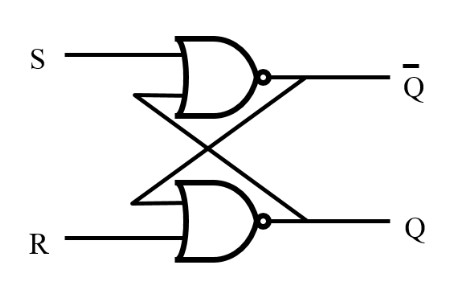

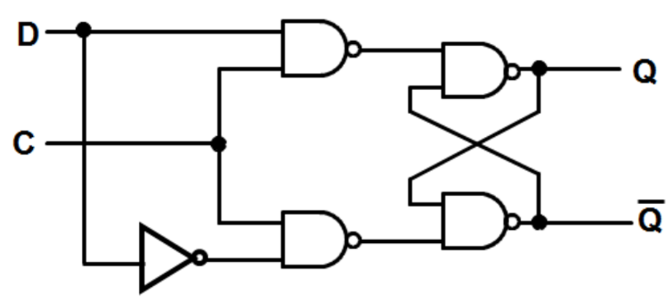

Bild 1: SR -spärr

Vad är en SR -spärr?

En SR-spärr, eller inställning av spärr, är ett grundläggande binärt lagringselement som tillhör kategorin av asynkrona kretsar.Till skillnad från synkrona kretsar fungerar SR -spärr utan en klocksignal och förlitar sig enbart på direkt kontroll av insignaler.Detta gör att de kan fungera oberoende inom digitala kretsar.En SR -spärr kan upprätthålla två stabila tillstånd: höga (1) och låg (0), vilket gör att den kan lagra en enda bit information tills den uppdateras av nya insignaler.

Att konstruera en SR-spärr involverar vanligtvis två tvärkopplade logikgrindar, vanligtvis eller grindar eller NAND-grindar.I en SR -spärrkonstruktion med NOR -grindar är utgången från varje grind ansluten till ingången till den andra och bildar en återkopplingsslinga.Denna konfiguration säkerställer att spärren snabbt kan ändra tillstånd baserat på insignalerna samtidigt som stabilitet upprätthålls tills en ny ingång uppmanar en förändring.

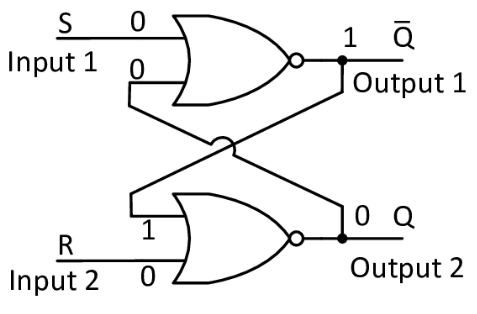

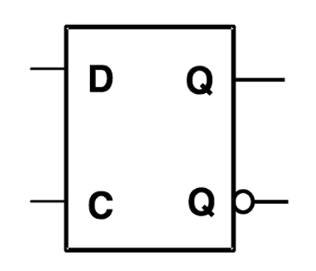

Bild 2: SR -spärr (2)

Ställ in ingångar: När inställningsingångarna är aktiverade (högt) växlar spärrutgången (q) till hög (1).

Återställ ingång (R): När återställningsingången (R) är aktiverad (hög) växlar utgången (Q) till låg (0).

Båda ingångarna höga: Om både S- och R -ingångar är höga samtidigt, kommer spärren in i ett odefinierat tillstånd, som bör undvikas i design.

SR -spärrar är viktiga för tillfällig datalagring och mellanresultat i digitala system.De är de grundläggande elementen i mer komplexa sekventiella kretsar som multi-bit-skiftregister, minnesenheter och vissa typer av räknare.

I dessa applikationer tillhandahåller SR -spärrar stabil datamängsel och kan snabbt svara på förändringar i externa signaler, vilket säkerställer en effektiv drift av hela elektroniska systemet.

En annan kritisk tillämpning av SR -spärrar är i feldetektering och korrigeringslogik inom digitala kretsar.På grund av deras förmåga att hålla ett stabilt tillstånd kan de övervaka systemstatusförändringar och snabbt återgå till ett fördefinierat säkert tillstånd när du upptäcker en anomali.Denna funktion är särskilt värdefull i system med hög tillförlitlighet som flyg- och medicinsk utrustning.

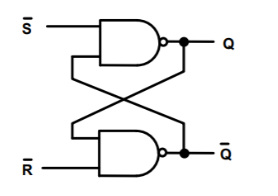

Symbol för SR -spärren

Att förstå dess symbol och struktur är grundläggande för att ta tag i dess drift och praktiska användning.I kretsdiagram har SR -spärren vanligtvis två huvudinmatningsportar märkta S (set) och R (återställning).Dessa ingångar styr spärrens utgångstillstånd, vanligtvis representerade som Q. Vissa mönster har också den omvända utgången, märkt Q ', vilket ger motsatt tillstånd av Q.

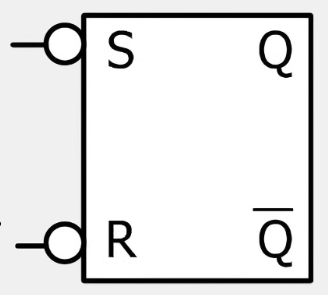

Bild 3: Symbol för SR -spärren

En SR -spärr representeras ofta av en rektangulär symbol med ingångar S och R och en utgång Q. I vissa fall visas också utgången Q '.Denna tydliga märkning gör det möjligt för kretsdesigners att snabbt identifiera komponentens funktion och dess roll inom den större kretsen.

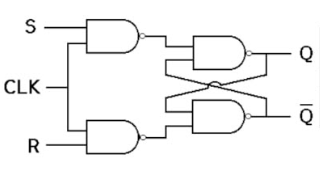

En vanlig variant av SR -spärren innehåller en klocka (CLK) ingång.CLK -ingången säkerställer att tillståndsförändringar inträffar i synkronisering med klocksignalen, vilket möjliggör exakt tidskontroll.I denna installation, även om S eller R är aktiverad, uppdateras spärrens tillstånd bara när CLK -signalen uppfyller specifika förhållanden, vanligtvis på den stigande eller fallande kanten.Detta förhindrar fel orsakade av insignalfel eller oavsiktliga ändringar.

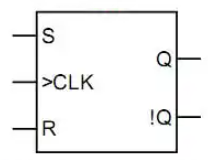

Bild 4: Symbol för den klockgrindade SR-spärren

Den klockade SR -spärrsymbolen inkluderar S-, R- och CLK -ingångarna inuti en rektangel.Denna standardiserade representation hjälper designers att förstå spärrens funktionalitet och dess tidsbehov.Till exempel, i högpresterande datoranvändning eller komplexa dataöverföringssystem, säkerställer noggrann CLK-kontroll data lagras och överförs exakt vid varje bearbetningssteg, vilket optimerar den totala systemets prestanda och tillförlitlighet.

Exakt kontroll av SR-spärringångar är viktig, särskilt vid utformning av höghastighets- och storkapacitetsminne eller tillfälliga databuffertar.Genom att utforma logikkretsar för att hantera S och R -aktivering kan komplexa funktioner såsom databelastning, rensning eller tillstånd återställning uppnås.Exakt CLK -signalkontroll säkerställer att alla dataoperationer följer en fördefinierad tidssekvens, vilket avsevärt förbättrar systemeffektiviteten och databehandlingsförmågan.

En djup förståelse av SR -spärrens symbol och struktur hjälper inte bara i korrekt kretskonstruktion och felsökning utan också genom att utföra komplexa digitala logiska operationer och förbättra systemprestanda.Detta är särskilt kritiskt i applikationer som kräver hög tillförlitlighet och exakt kontroll, såsom flyg- och medicinsk utrustning.

Typer av spärrar och deras arbetsprinciper

Spärr är grundläggande komponenter inom elektronisk design, som erbjuder olika funktioner och breda tillämpningar.Huvudtyperna av spärrar är SR -spärrar och D -spärrar, var och en med unika operationer och användningsfall.

SR -spärr

SR-spärren, eller inställning av spärr, är en grundläggande lagringsenhet som styrs av dess två ingångar, S (set) och R (återställning).

När S -ingången får en hög signal blir utgången Q hög, vilket indikerar att data är inställt.När R -ingången får en hög signal blir utgången Q låg, vilket indikerar att data återställs.Om både S- och R -ingångar är höga samtidigt, kommer spärren in i ett odefinierat tillstånd, vilket orsakar potentiell utgångsinstabilitet.Detta tillstånd måste undvikas i design.SR -spärrens direkta svar på insignaler gör det användbart i situationer som kräver snabb reaktion.

D spärr

D -spärren, även känd som en dataslås eller transparent spärr, erbjuder mer komplex kontroll med datainmatning D och klocksignal CLK.

Bild 5: D -spärr

Bild 6: D spärrssymbol

När CLK är hög följer utgången Q ingången D, vilket gör att data kan passera genom spärren fritt.När CLK går lågt är det nuvarande värdet på D låst och utgången Q förblir konstant tills nästa CLK -höga signal.Denna mekanism gör D -spärren idealisk för att tillfälligt lagra data för att synkronisera olika bearbetningshastigheter inom ett system.

SR- och D -spärrar har en oöverträffad roll i datalagring och tillståndsmaskinlogik.På grund av deras direkta insatsnivårespons är spärr väsentliga för att utforma asynkrona kretsar.De tillhandahåller viktiga funktioner för komplexa dataöverföringar och krafthanteringssystem och lagrar effektivt tillståndsinformation för att säkerställa en stabil drift.Korrekt användning av dessa spärrar kan förbättra kretsens tillförlitlighet och effektivitet, vilket gör dem nödvändiga i moderna elektroniska system.

Sanningstabellen för en SR -spärr

Bild 7: SR NAND LATCH

|

S |

R |

Q |

Q ' |

Notera |

|

0 |

0 |

1 |

1 |

FÖRBJUDEN |

|

0 |

1 |

1 |

0 |

UPPSÄTTNING |

|

1 |

0 |

0 |

1 |

ÅTERSTÄLLA |

|

1 |

1 |

Q |

Q ' |

BEHÅLLA |

Diagram 1: Sanningstabell över SR -spärr med NAND -grindar

Bild 8: SR eller spärr

|

S |

R |

Q |

Q ' |

Notera |

|

0 |

0 |

Q |

Q ' |

BEHÅLLA |

|

0 |

1 |

1 |

0 |

ÅTERSTÄLLA |

|

1 |

0 |

0 |

1 |

UPPSÄTTNING |

|

1 |

1 |

0 |

0 |

FÖRBJUDEN |

Diagram 2: Sanningstabell över SR -spärr med NOR -grindar

Nu tar vi sanningstabellen för SR -spärren med NOR -grind som ett exempel för att förstå innebörden av sanningstabellen för SR -spärren.

Input- och utgångstillstånd

Både S och R är 0: spärren förblir i sitt nuvarande tillstånd.Utgången Q förblir densamma, oavsett om den är 0 eller 1.

S är 0 och r är 1: spärren återställs, vilket tvingar utgången q till 0.

S är 1 och r är 0: spärruppsättningarna, vilket gör utgången q lika med 1.

Både S och R är 1: Detta tillstånd är ogiltigt eller odefinierat, ofta kallat det "förbjudna" tillståndet i en SR -spärr.I detta fall är Q och Q 'båda lika 0, vilket leder till en tvetydig utgång.

När S och R är båda 0, gör spärren ingenting och har helt enkelt sitt nuvarande värde.Detta är användbart för att upprätthålla staten utan förändringar.

När S är 0 och R är 1, berättas spärren uttryckligen att återställa, se till att Q är 0 oavsett dess tidigare tillstånd.Detta är ett enkelt sätt att rensa spärren.

När S är 1 och R är 0, är spärren inställd, vilket säkerställer att Q blir 1. Så här lagrar du en '1' i spärren.

När S och R är båda 1 är staten inte tillåtet eftersom det får båda utgångarna att vara 0, vilket är motsägelsefullt och opålitligt.Formgivare måste undvika detta tillstånd för att säkerställa en stabil drift.

Fördelar och nackdelar med spärr

Spärrar används ofta i digital kretsdesign på grund av deras enkelhet och låga kostnader.Dessa egenskaper gör det möjligt för spärr att arbeta med höga hastigheter med låg effektförbrukning, vilket gör dem idealiska för höghastighets digitala system.Till exempel, i processorregisterfiler, kan spärrar snabbt lagra och hämta data, vilket avsevärt ökar bearbetningshastigheten och effektiviteten.

Fördelar med spärr

Enkelhet och kostnadseffektivitet: spärrar är enkla komponenter som är billiga att implementera i digitala kretsar.

Hög hastighet och låg effekt: Deras design möjliggör snabb drift med minimal strömförbrukning, vilket är avgörande i höghastighets digitala system.

Effektivitet i datahantering: I applikationer som processorregistreringsfiler ger spärrar snabba datalagring och hämtning, vilket förbättrar den övergripande systemprestanda.

Nackdelar med spärr

Trots deras fördelar har spärr anmärkningsvärda begränsningar i vissa mönster och applikationer.

Oförutsägbart beteende i asynkrona mönster: Utan klocksignalkontroll kan spärrar bete sig oförutsägbart.I SR -spärrar, om både inställningar och återställning (R) ingångar är höga samtidigt, blir utgången odefinierad, vilket leder till instabilitet.Detta är problematiskt i realtidskontroll eller säkerhetskritiska applikationer, där tillförlitlig produktion är avgörande.

Komplex tidsdesign: Att designa med spärrar kräver noggranna tidsöverväganden.Ingenjörer måste redogöra för förseningar av signalutbredning och tävlingsförhållanden för att undvika tidsfel.Felaktig design kan resultera i dataförändringar innan klocksignalen stabiliseras, vilket orsakar datakorruption eller felaktig datafångst.Detta kräver en djup förståelse för tidsanalys och kretsbeteende.

För att hantera dessa utmaningar kan specifika designtekniker och strategier användas:

Synkroniseringsmekanismer: Att lägga till synkroniseringsmekanismer kan hjälpa till att hantera asynkrona ingångar och mildra oförutsägbart beteende.

Anpassad klockhantering: Implementering av anpassade klockhanteringsstrategier kan säkerställa att data är fastna korrekt och vid rätt tidpunkter.

Användning av EDA -verktyg: Modern Electronic Design Automation (EDA) -verktyg erbjuder avancerad analys och optimeringsfunktioner.Dessa verktyg hjälper till att förutsäga och lösa problem med timing och synkronisering under designfasen, vilket förbättrar tillförlitligheten och prestandan för digitala system med hjälp av spärrar.De hjälper designers att identifiera potentiella problem tidigt, vilket säkerställer att slutprodukten fungerar pålitligt under olika förhållanden.

Praktiska tillämpningar av SR -spärrar

SR -spärrar, kända för sin förmåga att snabbt och pålitligt upprätthålla tillstånd, används allmänt i olika elektroniska system.De utmärker sig i scenarier som kräver tillfällig datalagring eller tillståndsbehållning.

Tillfällig datalagring

SR -spärrar används ofta i cacheminne för att tillfälligt lagra data.Detta gör det möjligt för systemet att snabbt komma åt ofta använda data, vilket väsentligt ökar databehandlingsfunktionerna och effektiviteten hos storskaliga processorer.

Lagringsregisterfiler

I processorer möjliggör SR -spärrar snabb lagring och hämtning av data i registerfiler, förbättring av bearbetningshastighet och total systemprestanda.

Underhålla styrsignaler

I digitala kontrollsystem är SR -spärr användbara för att upprätthålla tillståndet för vissa styrsignaler tills externa förhållanden eller systemlogik dikterar en förändring.De hjälper också till att behålla stater inom systemet och säkerställa konsekvent prestanda i operationer som kräver precision och tillförlitlighet.

Trigger och motkretsar

SR-spärrbaserade flip-flops används ofta i kretsar som kräver synkroniserad drift, såsom digitala klockor och tidtagare.De kontrollerar greve -pulser och säkerställer exakt tidtagning och pålitlig prestanda.Dessa kretsar förlitar sig på SR -spärrar för att upprätthålla exakta räkningar, vilket underlättar tidpunkten och sekvensering i digitala system.

Mekaniska interaktioner

SR -spärrar är effektiva för att eliminera mekanisk studs i omkopplare.En mekanisk studs inträffar när en switch genererar snabba, repetitiva signaländringar på grund av dålig kontakt.SR -spärrar stabiliserar utsignalen och förhindrar fel orsakade av bullriga signaler.

SR-flip-flop

En SR-flip-flop, ofta kallad en kantutlösad inställning av inställningsflip-flop, består av två sammankopplade SR-spärrar.Denna struktur med dubbla spärr gör det möjligt att svara på specifika klocksignalkanter (antingen stigande eller fallande) för att ändra sitt tillstånd.Detta uppnås genom speciell logikkontroll mellan spärrarna.Utgången från den första spärren blir en del av ingången för den andra spärren, och utgången från den andra spärren påverkar i sin tur den första spärren, vilket skapar en sammankopplad återkopplingsslinga.

Bild 7: SR-flip-flop

SR-flip-flopen ändrar tillståndet exakt vid klocksignalens stigande eller fallande kant.Den sammankopplade återkopplingen mellan de två SR-spärrarna säkerställer att flip-flopen endast ändrar tillstånd som svar på klockkanten, vilket ger stabil och tillförlitlig utgång.

I mikroprocessorer och digitala signalprocessorer används SR-flip-flops för dataprovtagning och lagring.De fångar och stabiliserar data vid specifika klockkanter, vilket säkerställer tillförlitlig efterföljande databehandling och analys.

Kantutlösningsmekanismen hjälper till att undvika rasförhållanden, där olika delar av kretsen kan ändra tillstånd samtidigt utan synkronisering, vilket potentiellt kan leda till instabila eller felaktiga utgångar.SR-flip-flops är avgörande för att implementera specifik kommunikationsprotokolllogik, såsom ramsynkronisering och feldetektering.Deras stabilitet och snabb responstid hjälper till att upprätthålla dataöverföringskvalitet och systemtillförlitlighet.

Förbjudna tillstånd i SR-spärrar och SR-flip-flops

När vi utformar SR-spärrar och SR-flip-flops med NAND och NOR-grindar, måste vi alla vara uppmärksamma på att hantera och undvika hämmade tillstånd.Ett förbjudet tillstånd inträffar när både uppsättningarna (erna) och återställningar (R) är samtidigt höga (för NAND -grindar) eller låg (för eller grindar).Denna kombination leder till ett obestämd utgångstillstånd, eftersom utgången beror på kretsens tidigare tillstånd, vilket gör det oförutsägbart.

Förbjudna stater i Nand Gate SR -spärrar

När både S och R är låga går båda utgångarna högt, vilket bryter mot spärrens komplementära utgångskarakteristik.Detta resulterar i ett obestämt tillstånd.

Förbjudna stater i Nor Gate SR -spärrar

När både S och R är höga går båda utgångarna låga och skapar också ett obestämt tillstånd.Detta kan leda till oförutsägbart beteende i kretsen.

Praktiska tillvägagångssätt för att undvika förbjudna stater

Lägga till kontrolllogik

Använd ytterligare logikgrindar för att övervaka tillstånden i S och R. Om båda ingångarna trender mot ett förbjudet tillstånd, justera automatiskt en ingång för att förhindra det obestämda tillståndet.Detta säkerställer att utgångarna förblir stabila och förutsägbara.Implementera en logisk grind som ingriper när S och R är båda höga (eller låga), justering av en ingång för att upprätthålla ett giltigt tillstånd.

Programvarusimulering och hårdvarutestning

Utför grundliga programvaruimuleringar för att identifiera potentiella förbjudna tillstånd under olika driftsförhållanden.Detta gör att designers kan upptäcka och korrigera logiska fel innan fysisk implementering.Utför omfattande hårdvarutestning för att validera att kretsen hanterar alla ingångskombinationer korrekt.Detta steg hjälper till att säkerställa att spärren eller flip-flop fungerar pålitligt i verkliga scenarier.

Slutsats

Mångsidigheten och tillförlitligheten hos SR -spärrar understryker deras betydelse i digital kretsdesign.Genom att utforska det nyanserade beteendet hos SR -spärrar genom deras symbolrepresentationer, sanningstabeller och praktiska tillämpningar får vi en omfattande förståelse för deras drift och betydelse.Trots de potentiella fallgroparna från odefinierade tillstånd i asynkrona mönster kan strategisk implementering av kontrolllogik och omfattande simulering mildra dessa risker.Advanced Electronic Design Automation (EDA) -verktyg förbättrar ytterligare tillförlitligheten och prestandan för kretsar som innehåller SR -spärrar genom att förutsäga och lösa problem med timing och synkronisering.Oavsett om det används i tillfällig datalagring, kontrollsignalunderhåll eller feldetektering, visar SR -spärrarna vara grundläggande för att skapa robusta och effektiva digitala system.Deras roll i höghastighetsminnesoperationer och synkron databehandling i komplexa applikationer exemplifierar deras varaktiga relevans.När tekniken utvecklas fortsätter de principer som reglerar SR -spärrar att informera och inspirera innovationer inom digital elektronik, vilket säkerställer att dessa elementära komponenter förblir integrerade i utvecklingen av sofistikerade och pålitliga elektroniska enheter.

Vanliga frågor [FAQ]

1. Vad är en SR -spärr?

En SR-spärr, eller inställning av spärr, är ett grundläggande binärt lagringselement som används i digitala kretsar.Det är en asynkron krets, vilket innebär att den fungerar utan en klocksignal och förlitar sig på den direkta kontrollen av dess ingångar för att ändra tillstånd.

2. Vad är funktionen för SR i logik?

I logik styr SR (inställningsinmatning) ingångar spärren.

3. Vilken typ av logikport använder en SR -spärr?

En SR -spärr använder vanligtvis antingen eller Gates eller Nand Gates.I en NOR-grindbaserad SR-spärr matas utgången från varje eller grind tillbaka in i den andra ingången, vilket skapar en stabil återkopplingsslinga.I en NAND-grindbaserad SR-spärr används en liknande feedbackkonfiguration, men logiknivåerna är inverterade jämfört med NOR-grindbaserad spärr.Båda konfigurationerna uppnår samma grundläggande funktionalitet för att upprätthålla ett binärt tillstånd baserat på uppsättningen och återställningsingångarna.

4. Hur fungerar en spärr?

En spärr fungerar genom att använda feedback för att upprätthålla sitt utgångstillstånd baserat på de angivna ingångarna.I en SR -spärr kontrollerar uppsättningarna (erna) och återställningar (R) ingången (q).När inställningsingången är aktiverad (hög) är utgången inställd på hög (1).När återställningsingånget aktiveras (hög) återställs utgången till låg (0).Återkopplingsslingan i spärrens design säkerställer att när ett utgångstillstånd är etablerat förblir det stabilt tills en ny insignal ändrar den.

5. Vad är nackdelen med en SR -spärr?

Den primära nackdelen med en SR -spärr är det odefinierade tillståndet som inträffar när både uppsättningar och återställningsingångar är höga samtidigt.Detta tillstånd leder till ett obestämd utgångstillstånd, vilket kan orsaka instabilitet och oförutsägbart beteende i digitala kretsar.Detta "förbjudna" tillstånd måste undvikas i design för att säkerställa tillförlitlig drift.

SR-spärr, inställning av spärr, asynkron krets, binärt lagringselement, digitala kretsar eller grindar, NAND-grindar, återkopplingsslinga, högt tillstånd, lågt tillstånd, odefinierat tillstånd, klocksignal, direktkontroll, tillfällig datalagring, mellanliggande resultathållning, innehav,Feldetektering, flyg- och rymdapplikationer, medicinsk utrustning, kretskonstruktion, klockad SR-spärr, insignaler, symbol och struktur, höghastighetsminne, databuffertar, tidskontroll, exakt kontroll, tillståndsbehållning, mikroprocessorer, digitala signalprocessorer, dataprovtagning, datadataLagring, kantutlösad, SR-flip-flop, sammankoppling, rasförhållanden, kommunikationsprotokolllogik, ramsynkronisering, feldetektering, signalglitches, elektronisk designautomation, EDA-verktyg, synkroniseringsmekanismer, anpassad klockahantering, tidsframställningar, förökningsförändringar,Rasförhållanden, komplexa dataöverföringar, krafthanteringssystem, mekanisk studs, praktiska tillämpningar, digitala kontrollsystem, logikgrindar, programvarusimuleringar, hårdvarutestning, förbjudna tillstånd, spärrtillförlitlighet.