Innovativ guide till JK Flip-Flops: Analysera sanningstabeller, mekanismer och strategiska applikationer

Den här artikeln undersöker arkitekturen, driften och olika tillämpningar av JK-flip-flop, från dess grundläggande struktur och input-output-relationer, genom detaljerad operativ mekanik, till dess strategiska implementeringar i komplexa digitala system.Diskursen sträcker sig till att skilja mellan de kantutlösade och nivåutlösade varianterna och analysera deras respektive verktyg i synkrona och asynkrona miljöer.Katalog

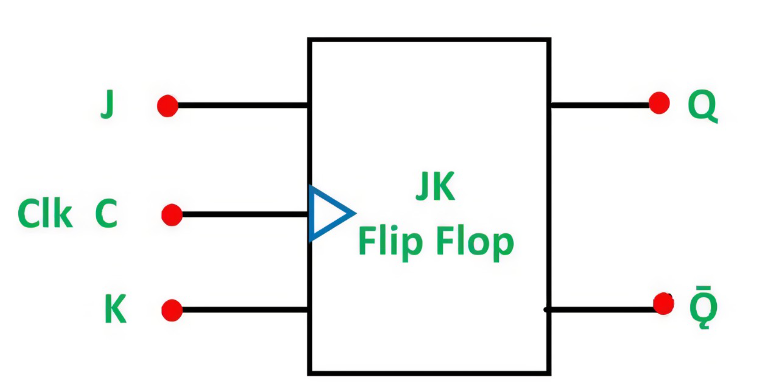

Bild 1: JK flip-flop

Grunder i JK-flip-flop

JK Flip-Flop är en grundläggande komponent inom digital elektronik, utformad för att lagra en enda information.Den bygger på den enklare SR-flip-flopen genom att lägga till feedback, vilket hjälper till att förhindra fel som kallas "rasförhållanden", där utgången blir instabil.

Denna flip-flop har två huvudingångar, j (set) och k (återställning), och två utgångar: q och dess komplement, q '.Dessa utgångar återspeglar kontinuerligt det nuvarande tillståndet och dess motsats, vilket gör att kretsen kan justera och svara på realtidsinmatningsändringar.

JK-flip-flopen fungerar på specifika sätt baserat på ingångsvärdena:

• När både J och K är 0: Flip-flopen har sitt nuvarande tillstånd.Inga förändringar inträffar.

• När både J och K är 1: Flip-flopen växlar sitt tillstånd.Om Q är 0 blir den 1;Om Q är 1 växlar den till 0. Denna växling är en nyckelfunktion som skiljer JK-flip-flop från enklare mönster.

• När J är 1 och K är 0: Flip-flopen sätter sitt tillstånd och gör Q lika med 1.

• När J är 0 och K är 1: Flip-flop återställs, vilket gör q lika med 0.

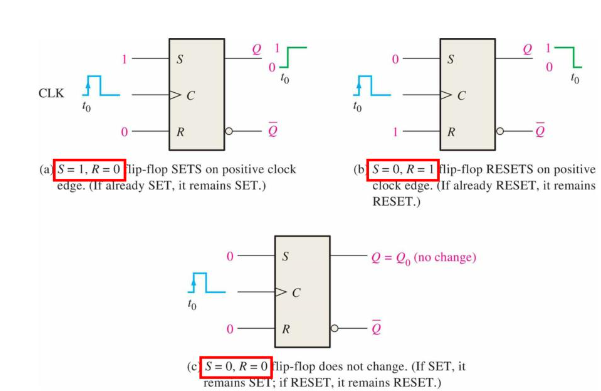

Drift av JK-flip-flop

JK-flip-flopen spelar en nyckelroll i digitala kretsar genom att hantera minne och timing genom ett koordinerat svar på insignaler och klockpulser.Driften beror starkt på tidpunkten för J- och K -ingångarna relativt klocksignalen, som bestämmer hur utgångstillståndet (Q och Q̅) förändras.Denna synkronisering säkerställer att flip-flopen uppför sig förutsägbart i olika kretsapplikationer.Flip-flopen förlitar sig på NAND eller NOR GATES för att hantera dessa statliga förändringar.

Håller det nuvarande tillståndet- När både J- och K-ingångar är låga (0) håller vipploppet sitt nuvarande tillstånd.Logikgrindarna "låser" utgångarna, vilket säkerställer att det tidigare tillståndet (antingen högt eller lågt) upprätthålls.Denna hållfunktion är allvarlig i applikationer där data måste förbli stabila tills en specifik förändring är ett måste.

Ställa in utgången High (Set State) -När klockpulsen inträffar och J är hög (1) medan K förblir låg (0), justeras logikgrindarna för att ställa in flip-flop.Detta driver utgången Q till ett högt tillstånd (1).Detta är användbart i situationer där kretsen måste utlösa en hög utgång, till exempel, aktivera en enhet eller lagra en "1" i minnet.

Rensa utgången låg (återställningstillstånd) - Om J är låg (0) och K är hög (1) vid en klockpuls övergår vipploppet till ett återställningstillstånd, vilket tvingar Q att gå lågt (0).Denna återställningsåtgärd används ofta i kretsar som behöver ett standard eller rensat tillstånd efter att ha slutfört en operation, till exempel rensning av data från minnet.

Växla utgången - Flip-flops unika funktion framträder när både J och K är höga (1).När klockpulsen anländer växlar vipplarna och byter utgången från dess nuvarande tillstånd till motsatt.Om Q är hög blir den låg och om Q är låg blir den hög.Denna växelfunktion är insisterande på applikationer som räknare eller enheter som måste växla automatiskt mellan tillstånd.

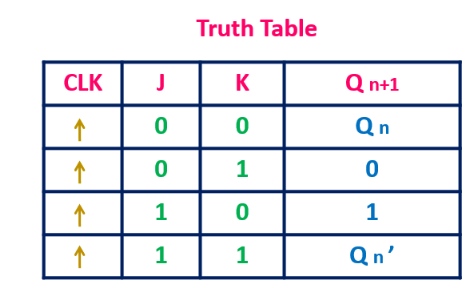

Bild 2: JK flip-flop sanningstabell

JK flip-flop sanningstabellanalys

Sanningstabellen för JK-flip-flop är ett viktigt verktyg för att visualisera hur den reagerar på olika insignaler synkroniserade med klockpulser.Denna tabell hjälper till att utforma och felsöka digitala kretsar genom att visa hur flip-flop-utgångarna förändras baserat på olika ingångsförhållanden.

• Både j och k låg (j = 0, k = 0): När båda ingångarna är 0, har vippan sitt nuvarande tillstånd.Oavsett om Q är hög eller låg, förblir den oförändrad.Detta är anmärkningsvärt för kretsar där stabil datamängden är önskad, till exempel element i minnet, där att bevara det aktuella tillståndet är lämpligt tills en specifik förändring utlöses.

• j hög, k låg (j = 1, k = 0): När J är 1 och K är 0 ställer vippan ut utgången Q till hög (1).Detta inställningsvillkor är användbart i applikationer som kräver en exakt trigger för att aktivera en operation, som att slå på en enhet eller initiera en sekvens i en logikkrets.

• j låg, k hög (j = 0, k = 1): Med J vid 0 och K vid 1 återställs vipplarna, vilket gör Q Low (0).Denna återställningsfunktion är allvarlig i system som måste återgå till ett standardtillstånd, som när du rensar data eller initialiserar en process.

• Både J och K High (J = 1, K = 1): När båda ingångarna är höga, växlar vipplarna sitt tillstånd.Om Q är hög blir den låg, och om Q är låg, växlar den till hög.Detta växlingsbeteende är betydande för enheter som måste växla mellan stater, till exempel i frekvensdelare eller räknare.

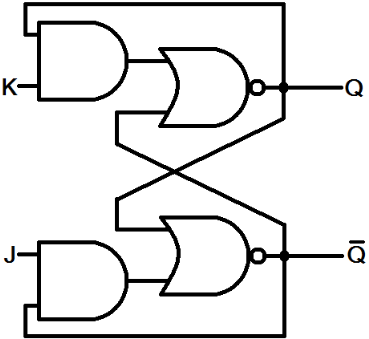

Bild 3: JK -spärr

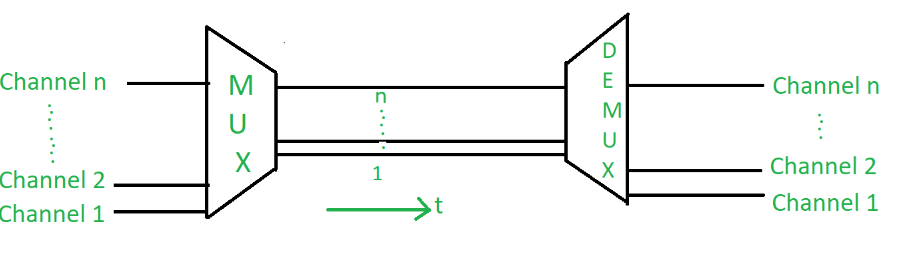

Insikter i JK -spärroperation och användning

JK-spärren fungerar på samma sätt som JK-flip-flop men utan behov av en klocksignal.Istället för att vänta på en klockkant, svarar JK-spärren kontinuerligt på att mata in förändringar, vilket gör den "nivåkänslig."Detta innebär att så länge ingångarna (J och K) är stabila kommer utgången att förändras i realtid och erbjuder omedelbar feedback baserat på ingångsförhållandena.

Till skillnad från den kantutlösade JK-flip-flopen, som uppdaterar dess utgång endast när klocksignalen ändras (från låg till hög eller vice versa), justerar JK-spärren sin utgång direkt när ingångar skiftar.Denna ständiga realtidens lyhördhet är värdefull i scenarier där omedelbar åtgärd önskas utan förseningen orsakad av klocksynkronisering.

Bullerfilter: I digitala kretsar som snabbt måste filtrera bort oönskat brus är JK -spärrens omedelbara reaktion på ingångsförändringar inflytelserik.Eftersom den inte väntar på en klockpuls kan den justera utgången så snart brus upptäcks, vilket förhindrar förseningar i signalkorrigering.

Enkla minneselement: JK -spärren kan fungera som en grundläggande minnesenhet i system som inte kräver komplex, klockad kontroll.Eftersom spärren håller utgången stabil så länge ingångarna inte förändras, har det effektivt det aktuella tillståndet, vilket är användbart för kretsar som behöver behålla information utan att kassera över klockor.

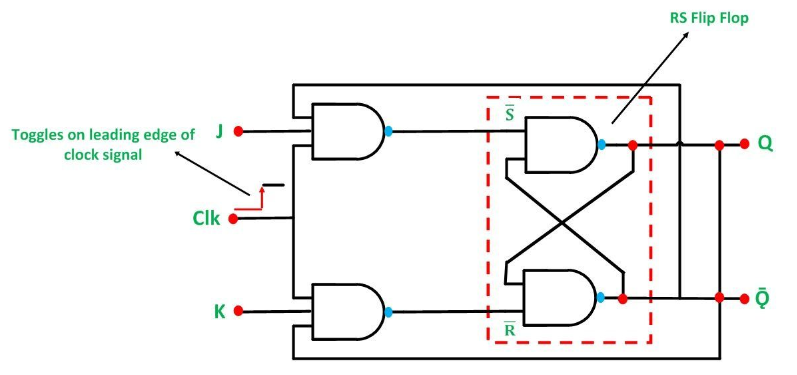

Bild 4: Tidsdiagramanalys för JK-flip-flop

Analysera tidsdiagrammet för JK-flip-flops

Ett timingdiagram över JK-flip-flop ger en visuell uppdelning av hur utgången svarar på olika ingångar, synkroniserade med klockans pulsövergångar.Detta diagram visar förhållandet mellan klocksignalen (CLK) och ingångarna (J och K) och hur de kollektivt påverkar utgångarna (Q och Q ').Det hjälper till att kartlägga flip-flops beteende över sekventiella tillstånd, vilket gör det lättare att förstå dess drift.

För det första diagrammet belyser att utgångarna endast uppdateras på klockans stigande eller fallande kanter.Denna funktion, känd som kantutlösande, är dominerande för JK Flip-flops operation.Det visar att även om ingångarna J och K ändras förblir utgången oförändrad tills klockkanten inträffar, vilket säkerställer förutsägbara och stabila övergångar.

Sedan, när diagrammet kartlägger variationerna av ingångar j och k, är det visuellt Visar hur varje ingångskombination påverkar utgången. Till exempel, när både J och K är låga (0), har utgången sitt nuvarande tillstånd.När J är hög och K är låg är utgången inställd.Denna tydliga visuella representation hjälper användare att förstå hur flip-flopen reagerar på olika inmatningskombinationer i realtid.

Slutligen, Tidsdiagrammet visar tydligt övergångarna mellan olika utgångstillstånd, vare sig de håller, ställer in, återställer eller växlar.Varje tillståndsförändring är bunden direkt till ingångsförhållandena och klockkanten, som visar en orsak-och-effekt-relation som är fokal för att utforma och felsöka kretsar.

Mångsidiga tillämpningar av JK-flip-flops

JK-flip-flops är kärnkomponenter i ett brett spektrum av digitala system, kända för sin flexibilitet och tillförlitlighet.Deras förmåga att hantera komplexa logiska operationer gör dem nödvändiga i flera viktiga applikationer, inklusive:

Bild 5: Minneslagring

JK-flip-flops används ofta för att lagra enskilda databitar, vilket gör dem till grundläggande element i minnesuppsättningar och register.Varje flip-flop har en bit, vilket säkerställer tillförlitlig datalagring, vilket är fördelaktigt vid utformningen av större minnessystem.

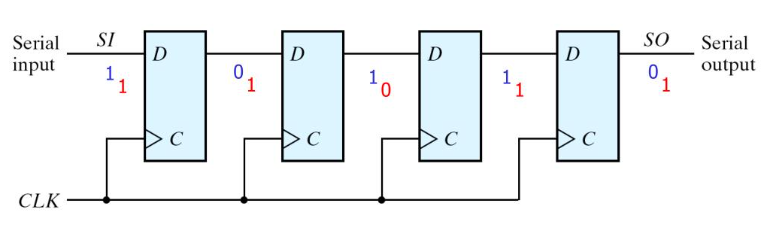

Bild 6: räknare och skiftregister

JK-flip-flops är dynamiska i sekvenseringsoperationer.De används allmänt i räknare för att räkna händelser eller pulser och i skiftregister för att konvertera seriedata till parallella format.Detta gör dem användbara för att hantera och manipulera data över olika stadier i en process, till exempel i kommunikationssystem.

Bild 7: Frekvensavdelning

Vid signalbehandling används JK-flip-flops ofta för frekvensdelning.Genom att växla sitt tillstånd med varje klockpuls delar de frekvensen för insignalen och skapar en långsammare och mer hanterbar klocksignal.Detta är anmärkningsvärt i applikationer som klocksignalhantering, där tidskontroll önskas.

Bild 8: Synkronisering

JK-flip-flops hjälper till att synkronisera flera digitala processer genom att säkerställa att olika delar av ett system fungerar tillsammans på ett samordnat sätt.De säkerställer att olika komponenter svarar korrekt på tidsinställda signaler och håller hela systemet synkroniserat.

Bild 9: JK flip-flop: kantutlösad och nivåutlösad

Olika typer av JK-flip-flops

JK-flip-flops finns i två huvudtyper: kantutlösad och nivåutlösad, var och en utformad för olika driftskrav.

Edge-triggered JK flip-flops: Ändra deras tillstånd endast vid specifika punkter - när klocksignalövergångarna från låg till hög (stigande kant) eller hög till låg (fallande kant).Denna egenskap gör dem idealiska för system där exakt tidpunkt är insisterande.Eftersom tillståndsförändringar inträffar exakt vid klockans kant, säkerställer dessa flip-flops att alla uppdateringar inträffar synkroniserade med klockpulsen.Detta förutsägbara beteende är dynamiskt i tätt kontrollerade miljöer som digitala klockor, register och de flesta sekventiella kretsar.Här är tidpunkten för varje förändring allvarlig för att upprätthålla systemstabilitet och se till att operationerna synkroniseras.

Nivåutlösad JK-flip-flops: fungerar annorlunda och reagerar på insignalen så länge klocksignalen är på en viss nivå - oavsett om den är hög eller låg.De väntar inte på en specifik klockaövergång.I stället, så länge ingången uppfyller de nödvändiga förhållandena, kommer flip-flopen att ändra tillstånd.Detta beteende gör nivåutlösade flip-flops bättre lämpade för asynkrona system, där ingångar kanske inte är i linje med en vanlig klockpuls.De ger flexibilitet i system där ingångar är oförutsägbara eller anländer till oregelbundna intervaller, till exempel i vissa signalbehandlingsuppgifter eller övervakningssystem som måste reagera omedelbart på förändrade ingångar.

För- och nackdelar med JK flip-flop

JK Flip-Flops erbjuder flera fördelar men kommer också med några avvägningar som måste vägas noggrant när du utformar digitala system.

|

Proffs |

|

|

Mångsidighet |

JK-flip-flops är mycket flexibla och kan

användas i olika digitala kretsar som minneslagring, räknare och

Kontrollsystem.De kan växla, ställa in eller återställa baserat på olika input

förhållanden, vilket gör dem lämpliga för ett brett utbud av applikationer som

kräver exakt kontroll över tillståndsövergångar. |

|

Självkorrigerande mekanism |

En av de framstående funktionerna i JK

Flip-flops är deras inbyggda återkopplingsslinga, som hjälper till att korrigera logiskt

säger dynamiskt.Denna självkorrigering säkerställer att kretsen kvarstår

Stabil under drift, även när ingångar förändras snabbt. |

|

Loppvillkor |

Till skillnad från enklare flip-flops, jk flip-flops

är utformade för att förhindra rasförhållanden - situationer där utgången blir

Instabil på grund av motstridiga insignaler.Denna förmåga att underhålla

Konsekvent utgång, även under snabba och sekventiella inmatningsändringar, förbättrar

Kretsens tillförlitlighet. |

|

Nackdelar |

|

|

Komplex design |

JK-flip-flops är mer komplicerade än

Grundläggande flip-flops.Deras design kräver ytterligare logikgrindar och input

övervakning, vilket kan göra kretsen svårare att designa och

Felsök, särskilt i system där enkelhet föredras. |

|

Utbredningsfördröjning |

Den interna grindningen används för att hantera tillstånd

Övergångar introducerar en försening i hur snabba signaler kan behandlas.I

Höghastighetsapplikationer kan denna försening påverka övergripande tidpunkt och sakta ner

Kretsens prestanda. |

|

Högre strömförbrukning |

På grund av deras komplexitet och behovet av

Övervaka ständigt inmatningsförhållanden, JK Flip-flops konsumerar mer kraft

Jämfört med enklare flip-flops.I större system eller kraftkänsliga

applikationer, denna högre kraftbehov kan bli en nackdel |

Bild 10: Master-Slave JK flip-flop

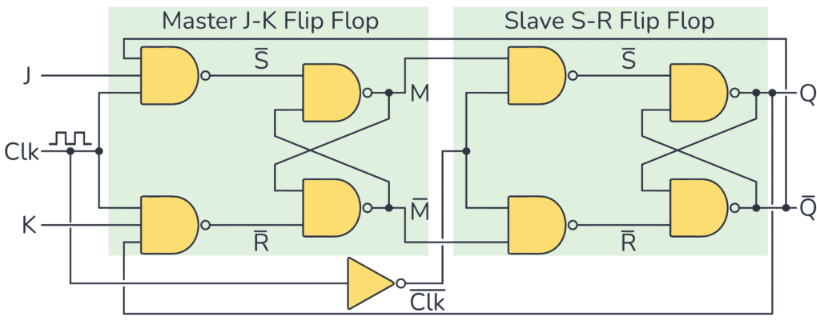

Avkodning av Master-Slave JK-flip-flop

Master-Slave JK Flip-Flop är utformad för att lösa det raundtillstånd som finns i standard JK-flip-flops genom att använda en tvåstegsprocess för att hantera ingångar och utgångar mer effektivt.

Det första steget, kallat master -scenen, fångar inmatningsvärdena när klocksignalen når en specifik kant, antingen stiger eller faller.Vid denna tidpunkt är inmatningsdata inlåst, vilket innebär att ytterligare förändringar av ingångarna inte påverkar det fångade tillståndet förrän nästa klockcykel.Detta steg säkerställer att flip-flop registrerar rätt ingång utan att påverkas av några efterföljande förändringar under samma klockcykel.

När masterfasen är klar kommer slavsteget att spela.Det här steget uppdaterar utgången baserad på de data som fångats av masterfasen, men endast vid nästa klockkant.Genom att separera ingångsfångsten från utgångsuppdateringen säkerställer slavsteget att utgången förblir stabil tills huvudstadiet har behandlat ingången helt.Detta förhindrar för tidiga eller oavsiktliga förändringar i utgången under klockcykeln.

Varför Master-Slave-konfigurationen är viktig?

Tvåstegsprocessen stabiliserar driften av JK-flip-flop, vilket förhindrar oönskade svängningar eller fluktuationer som kan hända i enklare konfigurationer, särskilt när båda ingångarna hålls höga.Genom att frikoppla ingångsbehandlingen från utgångsbytet säkerställer den master-slavkonfigurationen att utgångarna förblir förutsägbara och stabila, även i situationer där tidpunkten är värdefull.

Att ta itu med loppet runt villkor i JK-flip-flops

Tävlingsförhållanden förekommer i JK-flip-flops när båda ingångarna, J och K, är höga, och klocksignalen förblir aktiv för länge.Detta leder till kontinuerlig växling av utgångarna, vilket kan orsaka ojämnt beteende och störa kretsens tillförlitlighet.

Master-Slave-installationen använder en tvåstegsprocess för att förhindra ras-problem.Master -scenen fångar ingångsvärdena vid klockkanten och låser dem i. Slavsteget uppdaterar utgångarna vid nästa klockkant, vilket säkerställer att utgången inte ändras förrän ingångarna är helt bearbetade.Detta tillvägagångssätt förhindrar effektivt utgången från att växla okontrollerat, även om ingångarna förblir höga under en längre period.

En annan metod för att undvika tävlingsförhållanden är att justera klockpulsvaraktigheten.Genom att göra klockpulsen kortare än flip-flops förökningsfördröjning kan du se till att staten inte ändras mer än en gång inom samma klockcykel.Detta förhindrar att flip-flopen växlar upprepade gånger under en enda cykel, vilket stabiliserar utgången.

Dynamik för att byta i JK-flip-flops

Växlingsbeteendet för en JK-flip-flop drivs till stor del av tidpunkten för klocksignalen och ingångsnivåerna (J och K).Flip-flop ändrar tillstånd baserat på ingångarna som finns vid den positiva kanten på klocksignalen.I detta farliga ögonblick utvärderar flip-flop ingångarna och uppdaterar dess utgång i enlighet därmed.

När klocksignalen träffar den stigande kanten läser JK-flip-flop de nuvarande tillstånden för J- och K-ingångarna.Beroende på deras värden kommer flip-flop antingen att hålla, ställa in, återställa eller växla ut dess utgång.

Digitala klockor: Noggrannhet är allt i digitala klockor, och JK-flip-flops hjälper till att upprätthålla denna precision genom att säkerställa att tillståndsförändringar endast inträffar med exakta klockintervall.

Sekventiella logiska testare: I system som testar funktionaliteten för logikkretsar spelar JK-flip-flops en roll för att verifiera att varje komponent svarar korrekt på specifika tidsinställda signaler.

Andra tidskänsliga system: I olika digitala applikationer där tidpunkten är riskabel, såsom kommunikationssystem eller databehandlingsenheter, säkerställer JK-flip-flopen att tillståndsövergångar förekommer i synk med klockan, vilket förhindrar tidsfel.

Slutsats

JK-flip-flopen sticker ut som ett ultimat element i digital kretsdesign, och erbjuder en blandning av mångsidighet och precision desperat efter ett brett utbud av applikationer som sträcker sig från minneslagring till frekvensdelning och synkronisering av digitala processer.Dess förmåga att mildra rasförhållanden genom innovativa konfigurationer som Master-Slave-arrangemanget understryker dess anpassningsförmåga när det gäller att lösa inneboende designutmaningar.På samma sätt belyser flip-flops allvarliga roll för att säkerställa exakta tillståndsövergångar dess nödvändiga natur i skapandet och underhållet av pålitliga och effektiva digitala system.När tekniken utvecklas fortsätter de utvecklande mönster och tillämpningar av JK-flip-flopen att vara nyckeln till att driva gränserna för digital elektronik mot mer sofistikerade och robusta arkitekturer.

Vanliga frågor [FAQ]

1. Vilka är tillämpningarna av JK Flip Flop?

JK-flip-flop används i stor utsträckning i digital elektronik för en mängd olika uppgifter:

Timingapplikationer: Det kan fungera som ett fördröjningselement eller en timer när den är ansluten i vissa konfigurationer.

Räknare och register: Genom att växla sitt tillstånd med varje klockpuls används den för att utforma olika räknare och skiftregister som är ultimata i sekventiella logiska kretsar.

Minneslagring: Det tillhandahåller en grundläggande enhet för minneslagring, användbar vid lagring av bitar i beräkningar.

2. Hur fungerar en JK-flip-flop med en sanningstabell?

En JK-flip-flop har två ingångar (J och K) och en klocksignal.Driften varierar beroende på ingångstillstånd, synkroniserade till klockan:

• J = 0, K = 0: Utgången ändras inte.

• J = 0, K = 1: Utgången återställs till 0.

• J = 1, K = 0: Utgången är inställd på 1.

• J = 1, K = 1: Utgången växlar (dvs om den var 0 blir den 1 och vice versa).

3. Vad är JK Flip Flop och fungerar det?

En JK-flip-flop kombinerar egenskaperna hos SR- och T-flip-flops.Det undviker det "förbjudna" tillståndet som ses i SR-flip-flops genom att använda JK-ingångarna effektivt:

Flip-flops tillstånd styrs av ingångarna J och K, som avgör om utgången ska hålla, återställa, ställa in eller växla, synkronisera med den stigande eller fallande kanten på klockpulsen.

4. Vilka är tillämpningarna av spärr och flip-flops?

Datalagring: Spärrar och flip-flops är allvarliga för datalagring inom register och minnesuppsättningar.

Frekvensavdelning: Används i frekvensdelare på grund av deras förmåga att ändra tillstånd på klockkanter, halvera frekvensen med varje steg i en serie.

Statliga maskiner: Grundläggande vid utformning av ändliga tillståndsmaskiner som används för att implementera sekventiella logik- och kontrollkretsar.

Debouncing: Används för att stabilisera signaler från mekaniska switchar och knappar, säkerställa enstaka, rena övergångar.

5. Vad används flip-flops för?

Binär lagring: Varje flip-flop lagrar en bit data, vilket gör dem till byggstenar för binära lagringsenheter.

Klockavdelare: De delar upp ingångsklockfrekvensen med två, användbara i digitala klockor och tidtapplikationer.