HembloggDetaljerad guide till full adder

Detaljerad guide till full adder

Inom området för digital elektronik och datateknik representerar tilläggare en av de mest väsentliga byggstenarna, avgörande i konstruktionen och funktionaliteten hos mer intrikata aritmetiska kretsar.Som integrerade komponenter i den aritmetiska logikenheten (ALU) underlättar tilläggare många datoroperationer, allt från grundläggande aritmetik till komplexa logiska uppgifter som är nödvändiga för systemoperationer.Deras design, som kan variera från enkla halvåter till mer komplexa fulla adderare, spelar en avgörande roll för att förbättra effektiviteten och hastigheten för bearbetning inom digitala system.Den här artikeln fördjupar den detaljerade arkitekturen och funktionella nyanserna för olika typer av adders, illustrerar deras kritiska roll i modern datateknik och utforskar deras operativa logik, kretsar och applikationer inom det bredare sammanhanget av digital logikdesign.

Katalog

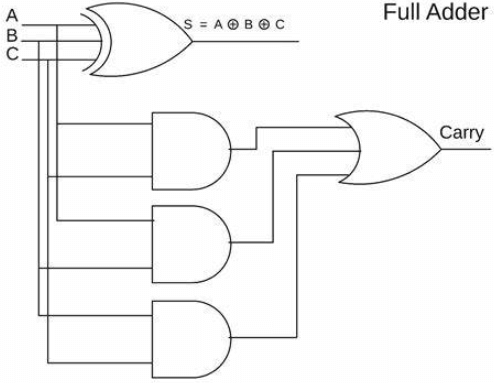

Bild 1: Full Adder

En adderare är en grundläggande komponent inom elektronisk teknik och digital logikdesign och spelar en central roll i mer komplexa datorsystem.Som en del av den aritmetiska logikenheten (ALU) hanterar addern en mängd väsentliga datoruppgifter.Effektiviteten och prestandan för hela processorn påverkas direkt av adderens design och funktionalitet.

I processorn används adderaren inte bara för grundläggande aritmetiska operationer som tillägg och subtraktion, utan den deltar också i ett bredare spektrum av logiska operationer.Till exempel, när man kör program, måste processorn ofta beräkna nya minnesadresser.Detta görs vanligtvis genom att lägga till eller subtrahera från den aktuella adressen - en uppgift som utförs av adderaren.De kontrollerar antalet sling -iterationer och det totala flödet genom att öka och minska räknare.I mer komplexa applikationer, såsom tabellindexering, lokaliserar tilläggare snabbt data genom att beräkna förskjutningar.Detta är viktigt för databashanteringssystem, kompilatorkonstruktion och storskalig databehandling.Tilläggare är också nyckeln till att implementera vissa kartläggningstekniker i cachesystem med flera nivåer, med hjälp av aritmetiska operationer för att bestämma datapositionen i cachen, vilket optimerar åtkomsteffektiviteten.

Teknologiskt implementeras tillägg genom olika kretskonstruktioner inklusive parallella, seriella och rörledare.Parallella tilläggare gynnas för sin förmåga att hantera flera siffror samtidigt, vilket gör dem lämpliga för scenarier som kräver snabb beräkning.Seriella adderare bearbetar å andra sidan en bit per klockcykel och är idealiska för resursbegränsade eller lågeffektmiljöer.Rörledare delar tilläggsprocessen i flera steg, var och en hanterar en del av tilläggsoperationen.Denna design ökar avsevärt beräkningshastigheten, särskilt i högpresterande datormiljöer.

En halvadderkrets är en grundläggande byggsten i digital elektronik, speciellt utformad för att lägga till två enstaka binära siffror.Denna krets utgör grunden för en full adder och är nyckeln till att förstå mer komplexa logikkretsdesign.I en halv adderare finns det två primära ingångar, märkta A och B, som representerar augend respektive tillägget.Denna installation gör det möjligt att beräkna summan och bära utgång utan behov av en bäringång från tidigare beräkningar.

Kärnan i en halvadder består av två logiska grindar: en XOR-grind och en och grind.Xor -porten ansvarar för att generera summan.Den fungerar under en enkel regel där den matar ut en 1 om bara en av dess ingångar är 1;Annars matar den ut en 0. och porten, å andra sidan, hanterar bärutgången.Det producerar en 1 endast när båda dess ingångar är 1, anpassar perfekt till de grundläggande kraven för binärt tillägg.

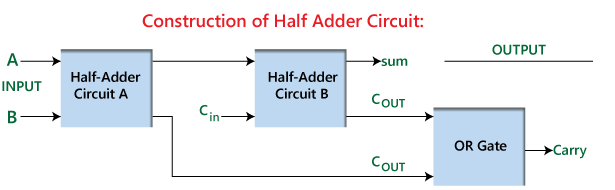

Bild 2: Konstruktion av halv adder

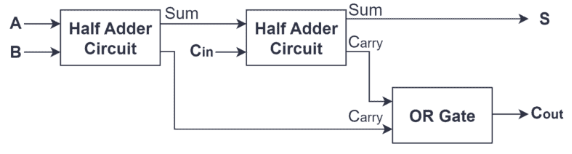

Denna effektiva och enkla design gör det möjligt för Half Adder att inte bara utföra grundläggande binärt tillägg oberoende utan också att fungera som en byggsten för att skapa en full adder.En fullständig adderare är konstruerad genom att kombinera två halva adderare med en extra eller grind.I denna installation tar den första halvleken den första tilläggsuppgiften och genererar en preliminär summa och bär.Den andra halvan Adder bearbetar sedan bärningen från den första tillsammans med en extra bäringång.Slutligen smälter OR -grinden de två bärutgångarna för att producera den slutliga bärutgången.Detta arrangemang förbättrar adderens funktionalitet, vilket gör att den kan hantera mer komplexa multi-bitars tilläggsuppgifter, visa upp den utbredda applikationen och betydelsen av halvtilldelare i digital kretsdesign.

En full adderare är en avancerad komponent i digital logikdesign, utrustad för att hantera tillägget av tre en-bitarnas binära ingångar, vanligtvis märkta som A, B och Carry-in (CIN).Denna design gör det möjligt för den fulla addern att effektivt bearbeta komplexa binära tillägg genom att integrera bärningen från tidigare beräkningar av lägre ordning i en enda operation.

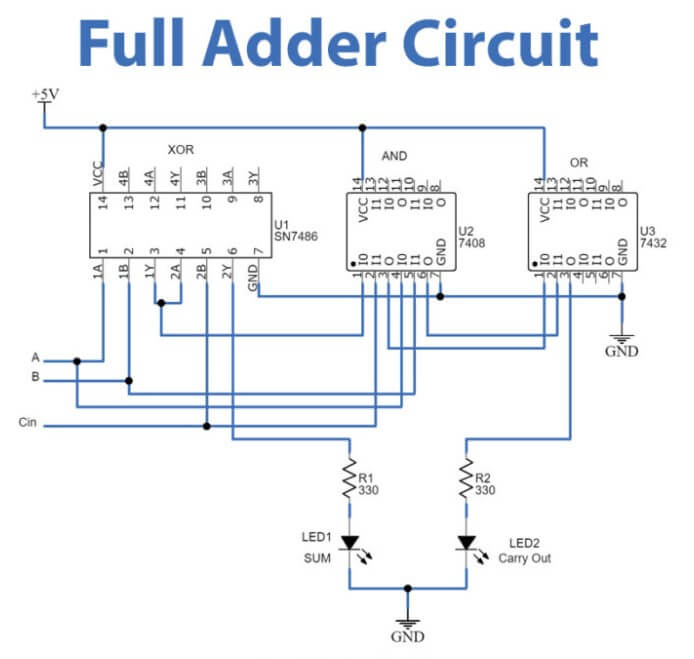

Bild 3: Full Adder Circuit

Funktionellt kan en full adderi mata ut en tvåsiffrig summa, vilket innebär att dess utgång kan variera från 0 till 3, och den kan också producera en utvärdering (COUT).This happens because, when all input bits are set to 1 (A=1, B=1, Cin=1), the sum output will be 1 (representing binary 01), and a carry-out of 1 is generated, indicating thatEn ytterligare bär måste överföras till nästa högre bit.

Strukturellt sett består hela addern i allmänhet av två hälftar och en eller grind.Den första halvleken tar ingångar A och B, genererar en initial summa och en signal.Denna initiala summa matas sedan, tillsammans med Carry-in (CIN), i den andra halvaddern.Den andra halvan Adders roll är att lägga till denna summa från första halvlek till CIN, producera en annan summa och en ny bärutgång.Samtidigt slås bärutgången från första halvlek och bärutgången från andra halvlek addern genom en OR-grind, som kulminerade med den slutliga utarbetandet (COUT) av hela adderaren.Utformningen av denna struktur säkerställer att den fulla addern effektivt hanterar utbredningen av bärare i tilläggsoperationer, vilket gör den idealisk för att utföra multi-bit binära tillägg.Således påskyndar utformningen av den fullständiga addern inte bara databehandling och förbättrar effektiviteten utan förenklar också komplexiteten i hårdvaruimplementering genom en enkel kombination av logiska grindar, vilket gör det till en oumbärlig komponent i multisiffrigt tillägg och den aritmetiska logikenheten (ALU: ALU (ALU).

|

Parametrar

|

Halv adder

|

Full adder

|

|

Beskrivning

|

Half Adder är en kombinationslogik

Krets som lägger till två 1-bitars siffror.Halvadderen producerar en summa av de två

ingångar.

|

En full adder är en kombinationslogik

Krets som utför en tilläggsoperation på tre en-bitars binära nummer.

Hela addern producerar en summa av de tre ingångarna och bärvärdet.

|

|

Föregående bär

|

Den föregående bären används inte.

|

Den föregående bärningen används.

|

|

Input

|

I en halv adder finns det två ingångsbitar (A,

B).

|

I full adder finns det tre ingångsbitar

(A, B, Ci).

|

|

Utgångar

|

Den genererade utgången är av två bitar-summa

och bär från inmatningen av 2 bitar.

|

Den genererade utgången är av två bitar-summa

och bär från inmatningen av 3 bitar.

|

|

Använd som

|

En halvadderkrets kan inte användas i

på samma sätt som en fulladderkrets.

|

En full adder -krets kan användas på plats

av en halv adder -krets.

|

|

Särdrag

|

Det är enkelt och enkelt att implementera

|

Utformningen av en full adder är inte som

Enkelt som en halv adder.

|

|

Logiskt uttryck

|

Logiskt uttryck för halv adder är:

S = a⊕b;C = a*b.

|

Logiskt uttryck för full adder är:

S = a⊕b⊕cin;Cut= (a*b)+(ci*(a⊕b)).

|

|

Logikgrindar

|

Den består av en ex-eller-grind och en och

gate.

|

Den består av två ex-eller, två och grindar,

och en eller grind.

|

|

Ansökningar

|

Det används i kalkylatorer, datorer,

Digitala mätanordningar etc.

|

Det används i flera bittillägg,

Digitala processorer, etc.

|

|

Alternativt namn

|

Det finns inget alternativt namn för hälften

huggorm.

|

En full adder är också känd som en krusningsbär

huggorm.

|

Diagram

1: Skillnad mellan halva addern och full adderare

Sanningstabellen för en full adderare är nyckeln till att förstå dess operativa logik och beskriver det exakta förhållandet mellan binära ingångskombinationer och deras motsvarande utgångar.Denna tabell visar alla potentiella ingångsscenarier och deras resultat, vilket gör det till ett viktigt verktyg för design och verifiering av digitala logikkretsar.Den fullständiga addern bearbetar tre ingångar: A, B och en carry-in (CIN), som var och en kan vara antingen 0 eller 1. Detta resulterar i åtta möjliga kombinationer av ingångar.

För var och en av dessa kombinationer inkluderar utgångarna från hela adderaren en summa (summa) och en utvärdering (cout).Summan är Modulo-2-tillägget (XOR-operation) för de tre ingångarna-A, B och CIN.Överföringen inträffar när minst två av ingångsbitarna är 1. Detta återspeglar den fulla adderens förmåga att hantera överföringen i sekventiella tilläggsoperationer, vilket säkerställer noggrannhet i beräkningar med högre bitar.

För att illustrera, överväg inmatningsscenariot där alla ingångar är 0 (a = 0, b = 0, c-in = 0).Utgångssumman kommer att vara 0, och bäret kommer också att vara 0, vilket indikerar att det inte finns någon extra summa eller bär att hantera.Om bara en ingångsbit är 1, till exempel A = 1, B = 0, C-in = 0, kommer utgångssumman att vara 1 utan bär, vilket visar att det inte finns något behov av att överföra en bär till en högre bit.När två ingångsbitar är 1, som A = 1, B = 1, C-in = 0, är utgångssumman 0 (eftersom 1+1 är lika med 2 i binär, och modulo-2 resulterar i 0), men transporten-Ut är 1, vilket indikerar en bär som måste överföras till nästa högre bit.Det mest komplexa scenariot inträffar när alla tre ingångsbitarna är 1 (a = 1, b = 1, c-in = 1);Utgångssumman är 1, och det finns en utförande av 1, vilket tyder på att transporthantering också kan krävas vid ännu högre bitar.

|

En

|

B

|

Ci

|

S

|

Cut

|

|

0

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

1

|

0

|

|

0

|

1

|

0

|

1

|

0

|

|

0

|

1

|

1

|

0

|

1

|

|

1

|

0

|

0

|

1

|

0

|

|

1

|

0

|

1

|

0

|

1

|

|

1

|

1

|

0

|

0

|

1

|

|

1

|

1

|

1

|

1

|

1

|

Diagram 2: Full adder sanningstabell

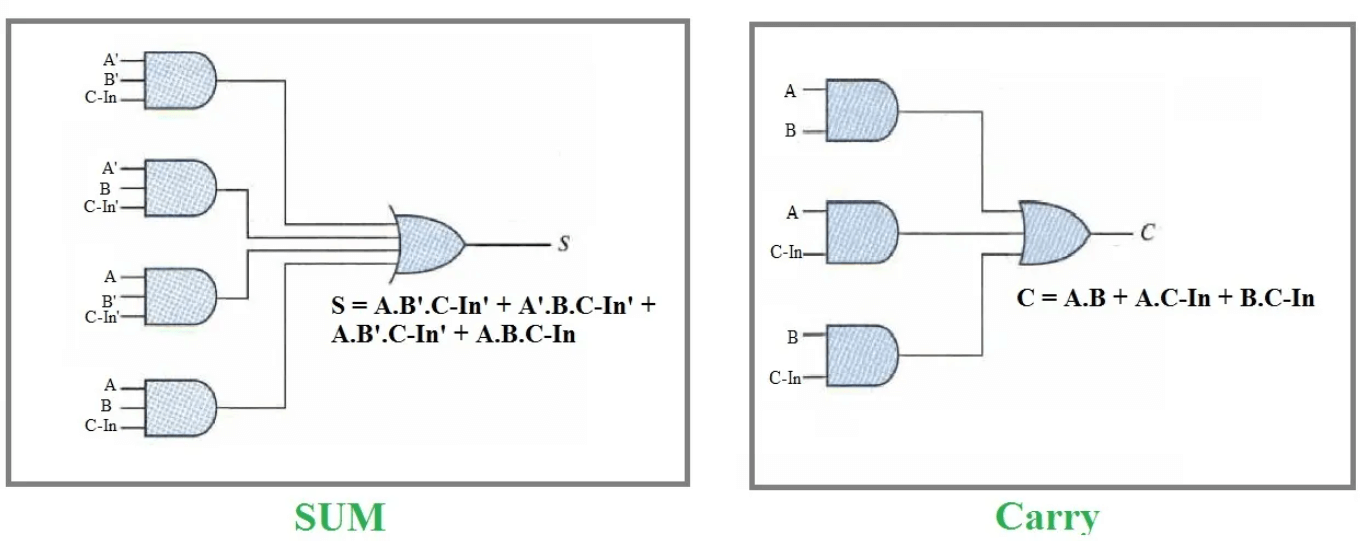

Att förstå hela addern innebär att dissekera sin funktionalitet med sanningstabellen, där olika kombinationer av ingångsvärden a, b och c-in leder till utgångar summa och cout.För att förstå operationen förenklar vi logikekvationerna steg för steg.

Logikuttryck för summan

Ekvationen börjar med de distinkta fall där summan är lika med 1:

• a 'b' cin + a 'b cin' + a b 'cin' + ab cin

Denna ekvation kan kondenseras genom att gruppera termer med och utan CIN:

• CIN (A 'B' + AB) + CIN '(A' B + A B ')

Denna förenkling leder till en lättare att implementera:

• Cin Xor (A XOR B)

Denna representation visar att SUM -utgången i huvudsak är XOR -operationen bland A, B och CIN, som fångar kärnbeteendet hos binärt tillägg där summan växlar baserat på ett udda antal.

Logik för cout

Börjar med förhållanden där bäret genereras:

• A 'B CIN + A B' CIN + AB C-IN ' + AB CIN

Förenkla ekvationen identifierar vi termer som vanligtvis innebär att generera en bär:

• AB + B Cin + en CIN

Letar du efter en annan metod för att implementera cout, kan ekvationen organiseras:

• AB + A CIN + B C-IN (A + A ')

Detta expanderar och rekombineras för att fånga alla scenarier där minst två ingångar är 1:

• AB CIN + AB + A C-IN + A 'B CIN

• AB (1 + CIN) + A C-IN + A 'B CIN

• AB + A C-IN (B + B ') + A' B CIN

• ab + a b 'cin + a' b cin

• AB + CIN (A 'B + A B')

Den slutliga kompaktformen för cout:

• AB + CIN (A XOR B)

Denna version av utvärderingsekvationen visar hur Cout produceras antingen när både A och B är 1, eller när en av A eller B är 1 tillsammans med en införande, och därmed inkapslar den logik som behövs för att hantera bärförökning i multi-lite binärt tillägg.Denna strömlinjeformade logik är särskilt användbar för att implementera effektiva digitala kretsar.

Bild 4: Ekvationer av en full adder

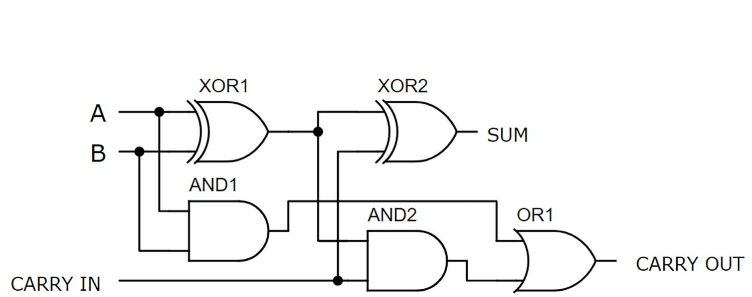

Implementering av en full adder-krets innebär att man noggrant monterar två halva tillsatser och en eller grind för att skapa en enhet som kan effektivt hantera tillägget av tre enbit-binära ingångar.Detta arrangemang optimerar kretsens komplexitet och säkerställer både effektiva och exakta beräkningar.

Till att starta tar den första halvan addern två primära binära ingångar, A och B, som är de viktigaste siffrorna som ska läggas till.Dess viktigaste uppgift är att beräkna summan och den första bärningen av dessa två siffror.Här levererar den första halvan addern två resultat: en initial summa (SUM1) och en initial carry (carry1).Sum1 härstammar från XOR -driften av A och B, vilket indikerar om det totala har ett udda antal 1.Carry1, resultatet av och driften mellan A och B, indikerar om båda siffrorna är 1, vilket kräver en bär till nästa högre bit.

Därefter går den andra halvan Adder till processen.Den använder sume-utgången SUM1 och den tredje ingången CIN (införande från en tidigare beräkning) som dess ingångar.Andra halvlek addern producerar två utgångar: det slutliga summan (SUM2) och den sekundära bär (bär2).Sum2, som är XOR -resultatet av SUM1 och CIN, representerar den sista summan av de tre ingångarna, som visar det aggregerade binära tillägget.Carry2, som kommer ut från och drift mellan SUM1 och CIN, indikerar en bär som genereras av dessa komponenter.

Bild 5: Full Adder Circuit med att använda två halv adder

Slutligen, för att slutföra hela adderens design, krävs en eller grind för att hantera bärutgångarna Carry1 och Carry2 från båda halvtilläggarna.Detta eller grind säkerställer att varje bär som genereras under beräkningarna vidarebefordras korrekt till den slutliga utgången.Därför är den fulla adderens slutliga bärutgång (COUT) OR -resultatet av carry1 och carry2.Införandet av detta eller grind garanterar att alla potentiella bärar beräknas exakt och förmedlas till nästa nivå i multi-bitars tilläggsoperationer, vilket säkerställer integriteten för den aritmetiska operationen över flera bitar.

Fullständiga adderare spelar en oumbärlig roll i digital logikdesign, och erbjuder många fördelar som gör dem väsentliga i olika datorer och databehandlingsscenarier.Deras främsta fördelar inkluderar anmärkningsvärd flexibilitet, snabba bearbetningshastigheter och effektiv bärhantering.Dessa egenskaper gör att fulla tillägg är idealiska för att utföra komplexa aritmetiska operationer och logiska funktioner, särskilt i applikationer som kräver sekventiell multi-bitars tillägg.

Fördelar

Flexibilitet: Fulltilläggare utmärker sig i sin förmåga att bearbeta flera binära ingångar (A, B och CIN) samtidigt.De kan också utvidgas till större adder -matriser för att hantera längre binära nummer.Denna skalbarhet är viktig för att bygga högpresterande aritmetiska logikenheter (ALUS), som måste utföra intrikata multi-bitar aritmetiska och logiska operationer.

Hastighet: Tack vare deras interna parallella bearbetningsarkitektur kan fullständiga tillägg slutföra tillägget av alla ingångar i en enda klockcykel samtidigt som de bestämmer sig för att bära utgångar.Denna kapacitet stöder kontinuerliga tilläggsoperationer och är nödvändig för realtidsdatabehandling i moderna mikroprocessorer och höghastighets datoranordningar.

Nackdelar

Men fullständiga tilläggare presenterar också anmärkningsvärda nackdelar:

Komplexitet i design och implementering: Fullständiga tilläggare involverar flera logiska grindar och förökning av flera nivåer, vilket gör deras designkomplex.Denna komplexitet ökar inte bara tillverkningskostnaderna utan kan också påverka kretsens tillförlitlighet.

Problem med fördröjning Fördröjning: Bär utbredning kan passera genom flera logiska grindar, var och en lägger till sin försening.Detta kan begränsa den totala beräkningshastigheten under storskaliga operationer, särskilt i omfattande datorsystem och i utformningen av mycket stor skala integration (VLSI) och höghastighetsprocessorer.Förseningen kan bli en betydande flaskhals i prestanda.

För att mildra dessa problem undersöker ingenjörer kontinuerligt effektivare kretskonstruktioner.Strategier inkluderar att använda snabbare logikgrindteknologier, optimera kretslayouter för att förkorta banlängder och utveckla avancerad teknik som transporter för att minimera förseningar i förökning.

Fullständiga tilläggare används i stor utsträckning i digital logik, uppskattade för sin flexibilitet och effektivitet, vilket gör dem centrala för en mängd dator- och databehandlingsuppgifter.Deras tillämpning sträcker sig från grundläggande aritmetiska operationer till komplex signalbehandling och systemkontroll.Här är en detaljerad titt på några viktiga områden där fullständiga tilläggare är integrerade.

Aritmetiska kretsar

En av de mest enkla användningarna av fulla adderare är i aritmetiska kretsar där de utför binärt tillägg.Speciellt avgörande för tillägg med flera bitars nummer, lyckas fulla tillägg längre binära sekvenser genom kaskad.I detta arrangemang hanterar varje full adder tillägget för sin bitposition och bäret från den nedre biten och passerar sedan den nya bärningen till nästa högre bit full adder.Denna kaskad möjliggör omfattande multi-bitstillägg över hela siffrans sortiment.

Databehandling

Fullständiga tilläggare spelar också en viktig roll i avancerade databehandlingsuppgifter som digital signalbehandling (DSP) för filtrering och Fourier -transformationer, där exakta och snabba aritmetiska operationer behövs.Dessutom, inom informationssäkerheten, inklusive datakryptering och feldetektering och korrigeringsalgoritmer som paritetskontroller och Cyclic Redundancy Check (CRC) -kodgenerering, är fullständiga tilläggs av avgörande för att utföra väsentliga bitoperationer.

Räknare

I digitala räknare är fullständiga adders nödvändiga för implementering av både öknings- och minskningsfunktioner, särskilt i modulära och synkrona räknare.De hanterar exakt bär och lånar för att säkerställa exakt räkning.

Multiplexers (MUX) och Demultiplexers (Demux)

Hos multiplexerare och demultiplexers spelar fullständiga adderare en avgörande roll i kanalval och datadistribution.De deltar i logiken som bestämmer vilka kanaler som används för datainmatning och utgång, vilket fattar beslut baserade på logikkontrollsignaler.

Minnesteknologi

I minnesadressering hjälper fullständiga tilläggare att generera adresssignaler för dynamiskt åtkomst till minnesplatser.Detta är särskilt viktigt i Dynamic Random Access Memory (DRAM) och andra lagringssystem, där fullständiga adderare stöder komplexa adressberäkningar för att förbättra effektiviteten i minnesåtkomst.

Aritmetiska logikenheter (ALU)

Slutligen, eftersom grundläggande komponenter i aritmetiska logikenheter i mikroprocessorer och digitala signalprocessorer, är fullständiga tilläggs avgörande.ALU hanterar alla aritmetiska och logiska operationer, med fulla tilläggare som säkerställer att data behandlas både snabbt och exakt.

Fulltillägg kan konstrueras med olika logikgrindar och konfigurationer.Här utforskar vi fyra olika implementeringar och belyser deras installation och operativa nyanser.

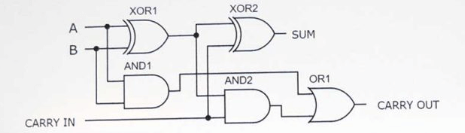

Full adder byggd med XOR och och eller grindar

Bild 6: Full adder byggd med XOR och och eller logikgrindar

Detta exempel visar en full adder byggd på en brödskiva med hjälp av diskreta transistorer.Konfigurationen omfattar fem logiska grindar: två XOR -grindar, två och grindar och en eller grind, som kräver totalt 21 transistorer.Ingångar A och B är anslutna till Breadboards upp till vänster och får en +5V -tillförsel.Dessa ingångar styrs med två växelomkopplare.Två lysdioder längst upp till vänster indikerar tillstånden för ingångar A och B, medan två lysdioder på höger sida visar utgångarna.Motståndet som används i kretsen är alla 2,2 000 ohm.När ingångar A och B är på och inbördet är av, visar utgången ett binärt värde på 10, vilket representerar summan 2 (1 + 1 + 0 = 10).Xor-grindarna, byggda med de första 12 transistorerna, hanterar den primära sammanfattningen, medan den nedre halvan av brödskivan innehåller och eller grindarna för transport, färgkodade ledningar förbättrar tydlighet och felsökning.

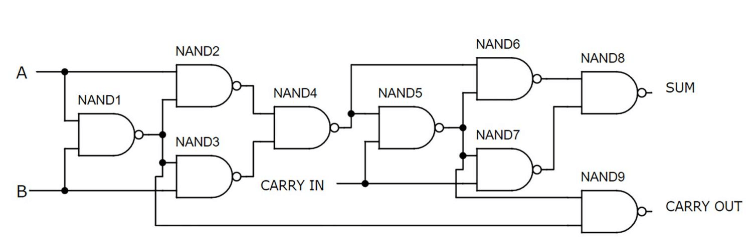

Full Adder med NAND -grindar

Bild 7: Full Adder med NAND -grindar

Denna fulla adder använder nio NAND -grindar, med varje grind gjord av två transistorer, totalt 18 transistorer.Denna metod är bland de enklaste och mest effektiva sätten att konstruera en full adder med diskreta komponenter.Alla grindarna är monterade på den övre halvan av brödskivan, medan switchar upptar den nedre halvan.Kretsens funktionalitet demonstreras med ingångar A och B på och inlärningen, vilket resulterar i ett utgångsbinärt värde på 10, motsvarande decimal 2.

Full Adder with Nor Gates

Bild 8: Full Adder with Nor Gates

Konstruerad med nio eller grindar, var och en kräver två transistorer, denna installation använder också totalt 18 transistorer.Att bygga en full addern med NOR -grindar erbjuder ett bra alternativ men innebär mer komplexa ledningar jämfört med NAND -grindar.Varje transistor i NOR -grindarna är jordade, med samlarna anslutna med orange jumpertrådar för att säkerställa snygga och organiserade ledningar.Denna konfiguration visas med ingångar A och B aktiverad och inaktiverad inaktiverad, vilket leder till utgångarna där bäret är aktivt och summan är av.

Under hela denna utforskning av addertekniken, från grundläggande halvtilldelare till sofistikerade fulla adderkonstruktioner, är det uppenbart att dessa komponenter är grundläggande för att främja digital elektronik.Exempel på operativa egenskaper och implementering gav understrykningens mångsidighet och effektivitet i olika beräkningsmiljöer.Genom att undersöka strukturerna och funktionen av adders, särskilt genom deras sanningstabeller och karakteristiska ekvationer, får vi värdefull insikt i deras kapacitet och begränsningar.Denna kunskap bidrar till att främja utformningen av effektivare och snabbare datorsystem.I slutändan förenklar inte bara tilläggskomplexa binära beräkningar utan möjliggör också spridningen av teknik i så olika områden som databehandling, minnesallokering och digital signalbehandling.När digital teknik utvecklas kommer den pågående förfining och innovation inom adderdesign att fortsätta att vara en hörnsten i utvecklingen av mer avancerade beräkningsarkitekturer, vilket säkerställer att dessa grundläggande komponenter förblir kärnan i digital systemdesign och implementering.

Vanliga frågor [FAQ]

1. Vad är en full adder -krets?

En full adderare är en digital krets som lägger till tre binära bitar för att producera en summa och en bärutgång.Det är utformat för att hantera tillägget av tre ingångar: två betydande bitar och en inbörd från ett tidigare tillägg.Detta gör att det kan användas i successiva steg för att lägga till multi-bitars binära nummer.

2. Hur många och, eller, Xor i full adder?

En typisk full adder innehåller:

Två XOR -grindar för att generera summan.

Två och grindar för att bidra till utförandeberäkningen.

En eller grind för att slutföra utgångsutdata.

3. Vad är bäringång i full adder?

Bäringången (CIN) i en full adderare är bärbiten från tillägget av de tidigare lägre betydande bitarna i multi-bitar binärt tillägg.Det gör det möjligt för den fulla addern att överväga denna tidigare bär när man beräknar den aktuella summan och den nya utrustningen.

4. Varför använda en full adder i stället för en halv adder?

En full addern används istället för en halv adder eftersom den kan lägga till tre bitar (inklusive bärningen från tidigare tillägg), vilket gör den lämplig för att kedja tillsammans för att lägga till multi-bitnummer.En halvadder kan bara lägga till två bitar och har inte en bestämmelse för en införande, vilket begränsar dess användning till de enklaste formerna av binär tillägg utan sekventiell bärutbredning.