En guide till grunderna i D -flip -flops - kretsar, sanningstabeller, typer, fördelar och begränsningar

I Digital Circuit Design används D-Type-flip-flops huvudsakligen i applikationer som kräver mycket stabil och exakt kontroll av dataflödet.För att djupt förstå beteendet och egenskaperna hos flip-flops av D-typ är konstruktion och analys av en sanningstabell ett kritiskt steg.Sanningstabeller hjälper inte bara att designers förutser kretsens svar, utan är också ett grundläggande verktyg för att optimera kretsdesign och feldiagnos.I den här artikeln kommer vi att utforska i detalj det specifika beteendet hos D-typen av flip-flop under olika ingångs- och klocksignalstillstånd, förklara svaret från dess interna logikgrindar genom exempel och hur man formulerar karakteristiska tabeller och karakteristiska ekvationer baserade påDenna information för att uppnå mer exakt kretsdesign och applikationer.Katalog

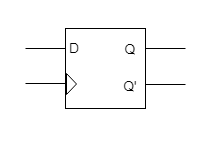

1. Arbetsprincip för D flip-flop

Innan vi börjar måste vi bygga en sanningstabell.Tabellen visar tydligt svaret på en D-flip-flop under olika ingångar (D) och klocksignalförhållanden.

Fall 1: D = 0

- • GATE 1 = 1

- • Gate 2 = 0

- • Gate 4 (Q (n+1) ') = 1

- • Gate 3 (Q (n+1)) = 0

Om D är låg (0) kommer Q -utgången också att vara låg (0).Eftersom en av ingångarna till grinden 4 är 0, och grind 4 är en NAND -grind, kommer dess utgång att vara 1 oavsett de andra ingångarna på grund av NAND -portens natur.

Fall 2: D = 1

- • Gate 1 = 0

- • GATE 2 = 1

- • Gate 3 (Q (n+1)) = 1

- • Gate 4 (Q (n+1) ') = 0

Om d är hög (1) kommer Q -utgången att gå högt (1) oavsett dess tidigare tillstånd.Eftersom en av ingångarna till grinden 3 är 0, och grind 3 är en NAND -grind, kommer dess utgång att vara 1 oavsett de andra ingångarna på grund av NAND -portens natur.

2. Situationsanalys och sanningstabellkonstruktion

När man undersöker hur en flip-flop av D-typ svarar på olika inmatningsförhållanden är ett mycket kritiskt steg att konstruera och förstå en sanningstabell.Detta hjälper oss att förutsäga kretsbeteende och är grunden för felsökning och designoptimering.Först ställer vi in klocksignalen till en kontinuerlig hög nivå (1).Detta innebär att flip-flopen svarar på ingången vid D och uppdaterar utgången vid Q i enlighet därmed.

Analysera situationen när D -ingången är låg (0):

- Drift: Ställ in D -terminalen på 0, observera och registrera ändringarna i utgången.

- Logic Gate Response: I denna installation är Logic Gate 1 inställd på att mata ut en hög nivå (1), medan Logic Gate 2 matar ut en låg nivå (0).

- Utgångspåverkan: Eftersom NAND -porten (GATE4) får minst en låg nivå (0), enligt NAND -portens egenskaper, är dess utgång hög nivå (1).Samtidigt är utgången från NAND -porten 3 låg (0).

- Slutlig Q -utgång: Detta resulterar i att Q (n+1) 'är hög (1) och Q (n+1) är låg (0).

Analysera situationen när D -ingången är hög (1):

- Operation: Ställ in Terminal på 1 just nu.

- Logic Gate Response: Gate 1 matar nu ut (0) och grind 2 -utgångar hög (1).

- Utgångspåverkan: Samtidigt får NAND GATE 3 minst en låg nivå (0), vilket gör att dess utgång blir hög (1), medan utgången från NAND -porten 4 är låg (0).

- Slutlig Q -utgång: Resultatet är att Q (n+1) går högt (1), medan Q (n+1) 'förblir låg (0).

Enligt ovanstående två situationer väntar vi till sanningstabellen för D-flip-flop

|

Klk |

D |

Q (n+1) |

Ange |

|

- |

0 |

0 |

ÅTERSTÄLLA |

|

- |

1 |

1 |

UPPSÄTTNING |

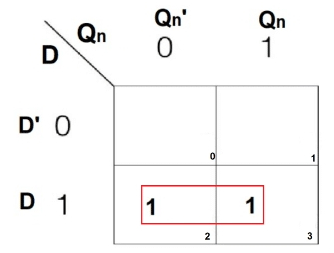

Vi kan sedan skriva egenskapstabellen för D-flip-flopen baserat på denna sanningstabell.I sanningstabellen kan du se att det bara finns en ingång D och en utgång Q (n+1).Men i funktionstabellen ser du att det finns två ingångar D och Q N och en utgång Q (n+1).

Det framgår av ovanstående logikdiagram att Qn och Qn 'är två komplementära utgångar som också fungerar som ingångar till GATE3 och GATE4, så vi betraktar QN (dvs. det nuvarande tillståndet för flip-flop) som en ingång, och Q (n+1) är nästa tillstånd som utgången.

Efter att ha skrivit den karakteristiska tabellen kommer vi att rita en 2-variabel K-plot för att härleda den karakteristiska ekvationen.

|

D |

Qn |

Q (n+1) |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

Från K-kartan får du 2 par.Efter att ha löst båda får vi följande karakteristiska ekvation:

Q (n+1) = D

3. Typer av flip-flops av D-typ

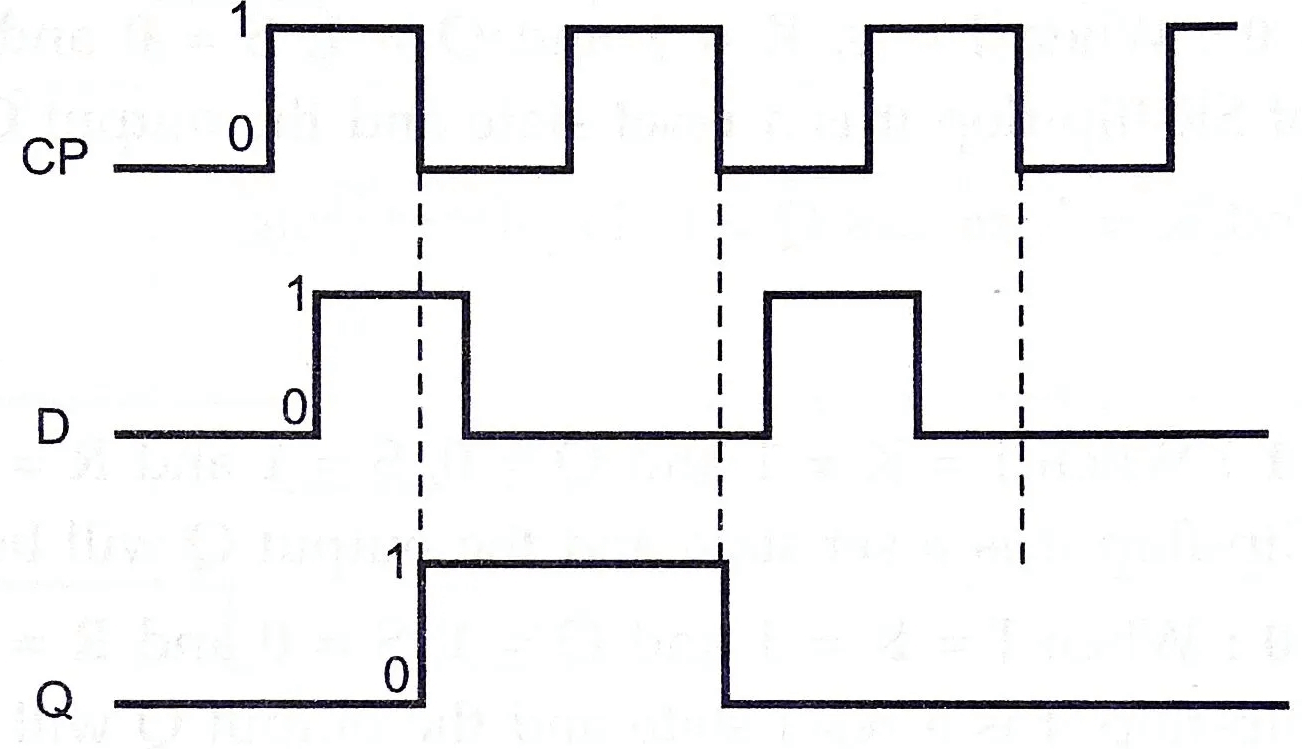

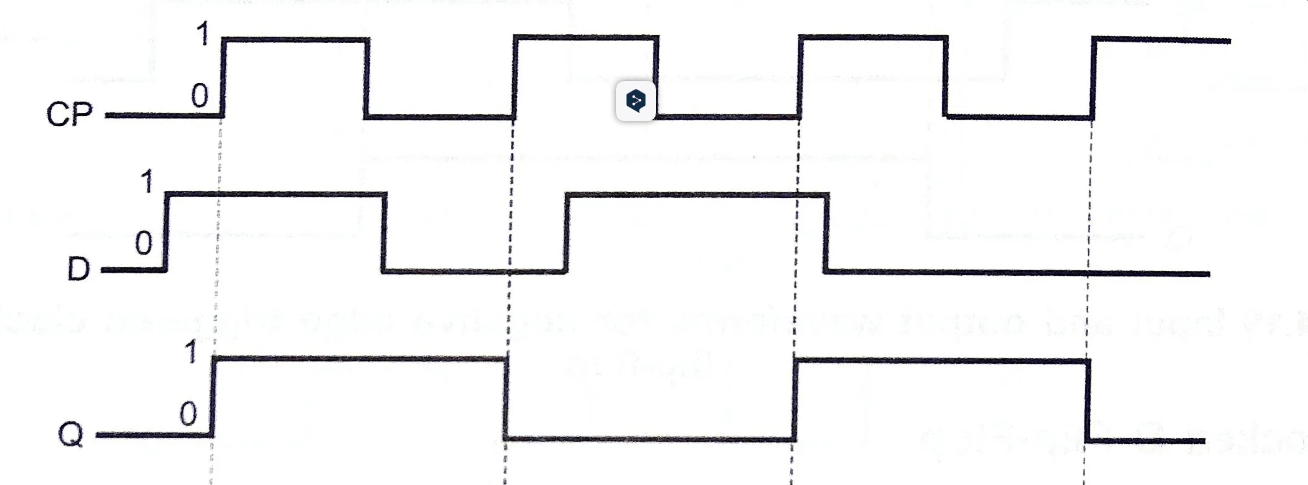

Beroende på hur klocksignalen tas emot kan D-flip-flops delas upp i två kategorier: nivåutlösad och kantutlösad.Varje typ har specifika funktioner och lämpliga applikationer.

Nivåutlösed D flip-flop (spärr)

Nivåutlösade D-flip-flops, allmänt kända som spärrar, är känsliga för de höga och låga nivåerna på klocksignalen.Så här fungerar det:

- • När klocksignalen ställs in hög (1) och ingången till D -terminalen ändras återspeglar utgången från Q -terminalen samma tillstånd nästan omedelbart.Detta innebär att eventuella ändringar vid D kommer att återspeglas direkt vid Q.

- • När klocksignalen är låg (0) förblir utgången vid Q densamma oavsett vad som händer med D -terminalen.

Denna typ av trigger är idealisk för applikationer som kräver stabil datautgång, till exempel tillfälligt lagring av data i ett datainsamlingssystem.Spärren behåller sitt tillstånd tills klocksignalen ändras, vilket säkerställer konsistensen för datautgången.

Positiv kant utlöste D flip-flop

En positiv kantutlösed D-flip-flop svarar endast när klocksignalen övergår från låg till hög.Lär dig hur det fungerar:

- • Fokusera på att övervaka klocksignalens stigande kant.

- • Omedelbart efter upptäckt av den stigande kanten överförs data på D -terminalen till Q -terminalen.

Denna typ av flip-flop är lämplig för applikationer som kräver exakt fångst av data vid ett specifikt ögonblick, vanligtvis i synkrona kretsar.

Negativ kant utlöste D flip-flop

Den negativa kanten som utlöses D-flip-flop är motsatsen till den positiva kanten utlöst typ och svarar på den fallande kanten på klocksignalen.Så här fungerar det:

- • Övervaka klocksignalen för fallande kanter.

- • När klocksignalen övergår från hög nivå till låg nivå fångas och överförs det nuvarande tillståndet för D -terminal till Q -terminal.

Denna typ av flip-flop används i applikationer där data måste fångas i det exakta ögonblicket som klocksignalen faller för att säkerställa exakt tidpunkt i olika digitala system.

4. Fördelar och begränsningar av flip-flops av D-typ

Fördelar

Förenklad design: D flip-flop har en enda datainmatning, vilket förenklar den övergripande kretskonstruktionen.Detta minskar anslutningsfel och påskyndar implementeringen av layout, särskilt under snabb prototypning av komplexa kretsar.När man arbetar med komplexa mönster innebär färre anslutningar mindre potential för fel, vilket gör processen mjukare och effektivare.

Stabilitet och tillförlitlighet: Utformningen av D-flip-flop eliminerar återkopplingsslingor, vilket gör det mindre mottagligt för rasförhållanden och brus.Till exempel säkerställer d-flipens robusthet konsekvent prestanda i miljöer med svår elektrisk störning.

Låg effektförbrukning: D flip-flops konsumerar mindre kraft jämfört med andra flip-flops.Detta förlänger batteritiden och minskar driftskostnaderna, vilket gör det idealiskt för bärbar och fjärrövervakningsutrustning.I batteridrivna system kan användning av en D-flip-flop avsevärt förlänga enhetens livslängd.

Bistable Operation: D flip-flops kan underhålla sitt tillstånd utan att ändra insignalen, vilket gör dem mycket användbara i applikationer som kräver långsiktig statlig retention, vilket kan vara mycket värdefullt för automatiserade kontroll- och säkerhetssystem.

Begränsningar

Brist på återkopplingskontroll: D flip-flops har ingen inbyggd återkopplingsväg, vilket gör dem olämpliga för system som kräver dynamisk utgångsjustering, såsom servomotorstyrning eller adaptiv signalbehandling.Denna begränsning kan vara viktig i applikationer som kräver kontinuerlig feedback för att justera utgången i realtid.

Förökningsfördröjning: Även om D-flip-flops i allmänhet svarar snabbt uppvisar de fortfarande viss fördröjning.I höghastighets digitala kommunikationssystem kan denna försening orsaka datasynkroniseringsproblem.Formgivare måste redogöra för denna försening för att undvika tidsfel i snabba miljöer.

Skalbarhetsproblem: Även om D-flip-flops är lämpliga för många standardapplikationer, kan de möta utmaningar när de skalar till mer komplexa digitala system.Att hantera mer samtidiga signaler eller högre datahastigheter kan komplicera systemdesign, vilket ökar svårigheten och kostnaden.När systemkomplexiteten ökar blir begränsningarna för D-flip-flops för att hantera stora mängder signalbehandling tydligare.

5. Ansökningsområden

D flip-flops har en mängd praktiska tillämpningar i digitala system.Vissa nyckelanvändningar inkluderar:

Skiftregister: Genom att kaskera flera D-flip-flops kan du skapa skiftregister som lagrar och skifter data i digitala system.Skiftregister används ofta i seriekommunikationsprotokoll som UART, SPI och I2C.I praktiken kan du använda dem för att konvertera data mellan serie- och parallella former, vilket underlättar effektiv dataöverföring.

Tillståndsmaskin: D flip-flops är en integrerad del av att implementera en tillståndsmaskin, som styr händelsens sekvens i ett digitalt system.Statliga maskiner är allestädes närvarande i kontrollsystem, bilapplikationer och industriell automatisering.I en automatiserad produktionslinje kan till exempel en tillståndsmaskin hantera verksamhetssekvensen, vilket säkerställer att varje steg körs i ordning.

Räknare: Att kombinera D-flip-flops med andra digitala logikgrindar kan skapa binära räknare som räknas upp eller ner beroende på designkraven.Dessa räknare är avgörande i realtidsapplikationer som tidtagare och klockor.Till exempel, i en digital klocka, hjälper en räknare att spåra tidens gång genom att räkna klockpulser.

Datalagring: D flip-flops kan lagra tillfälliga data i digitala system.De används ofta med andra lagringselement för att bygga mer komplexa lagringssystem.I en dators minnesarkitektur kan till exempel en D-flip-flop tillfälligt lagra bitar av data som en del av en större minnesstruktur.

6. Sammanfattning

Oavsett om det är i olika praktiska tillämpningar som datalagring, tillståndskontroll eller exakt tidpunkt, har D-typ flip-flops visat sin kraftfulla funktionalitet.Deras design förenklar kretskomplexiteten, förbättrar systemstabiliteten och tillförlitligheten och minskar kraftförbrukningen.Som designer kommer att förstå de detaljerade arbetsmekanismerna och potentiella tillämpningarna av dessa flip-flops att hjälpa dig att bättre använda dessa enheter för att lösa specifika tekniska utmaningar och därmed utforma effektivare och pålitliga digitala system.

Jag hoppas att den här artikeln är till hjälp för dig.Om du behöver utforska mer teknisk kunskap om flip-flops av D-typ kan du kontakta oss.

Vanliga frågor [FAQ]

1. Hur fungerar en D-flip-flop?

D flip-flop (D flip-flop) är en elektronisk komponent som huvudsakligen används för att lagra signaltillstånd.På den stigande kanten av klocksignalen läser och spärrar D-flip-flopen signaltillståndet vid D-ingången tills nästa stigande kant av klocksignalen.Specifikt, om D -terminalingånget är hög nivå (1), kommer utgången Q också att bli hög nivå efter klockpulsen;Om D -terminalen är låg nivå (0) kommer utgången Q att bli låg nivå..

2. Vad står D i D flip-flop för?

"D" i D flip-flop står för "data", vilket innebär att denna flip-flop huvudsakligen används för lagring och överföring av data.

3. Vad är utgångsfrekvensen för D-flip-flop?

Utgångsfrekvensen för en D-flip-flop är lika med hälften av insatsen.Detta beror på att D-flip-flopen bara svarar på en kant av signalen (vanligtvis den stigande kanten) i varje klockcykel, så data uppdateras endast en gång varannan klockcykler.

4. Vad är skillnaden mellan en D-flip-flop och en T-flip-flop?

Den största skillnaden mellan D-flip-flop och t flip-flop är deras funktion och syfte.D flip-flops används för att låsa en enda datatbit och är idealiska för datalagring och signalsynkronisering.T-flip-flop (vipploppflip-flop) växlar sitt utgångstillstånd vid varje klockpuls.Om ingången är hög nivå kommer utgången att växla från hög nivå till låg nivå eller från låg nivå till hög nivå.Flat, som gör T-flip-flops som vanligtvis används i motdesign.

5. Varför använder vi en D-flip-flop istället för SR-flip-flop?

Vi föredrar att använda D-flip-flops istället för SR-flip-flops (inställning av flip-flop), främst för att D-flip-flops är enklare och säkrare i design.SR-flip-flop måste styra uppsättningen och återställa signaler samtidigt.Om båda ingångarna är höga på samma gång kommer det att få utgången att ange ett instabilt tillstånd, vilket kan orsaka problem i praktiska applikationer.Däremot kräver D-flip-flopen endast en datainmatning, är lättare att kontrollera och verkar inte instabil.Därför är D-flip-flopen mer föredragen i applikationer som kräver stabil datalagring och förenklad design.